勇敢的芯伴你玩转Altera FPGA连载49:PWM蜂鸣器驱动之引脚分配

0赞勇敢的芯伴你玩转Altera FPGA连载49:PWM蜂鸣器驱动之引脚分配

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1i5LMUUD

PlanAead引脚分配

这个例程的顶层源码里有3个接口,即:

input ext_clk_25m, //外部输入25MHz时钟信号

input ext_rst_n, //外部输入复位信号,低电平有效

output reg beep //蜂鸣器控制信号,1--响,0--不响

这3个信号都是FPGA引脚上定义和外部设备连接的信号,因此我们需要将这些信号和FPGA的引脚进行映射。

如图7.5所示,点击Quartus II菜单上的“Assignments à Pin Planner”选项。

图7.5 Pin Planner菜单

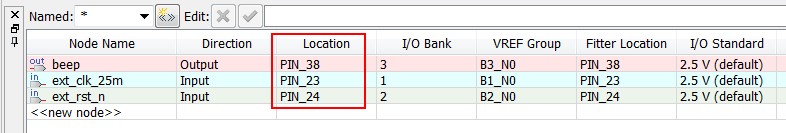

如图7.6所示,在Pin Planner界面最下面出现的“Node Name”一列中,有我们的3个信号接口,这里“Location”一列可以输入它们对应FPGA的引脚;“I/O Standard”一列可以输入I/O电平标准,默认虽然是2.5V,但由于我们原理图上已经把VCCIO连接3.3V,所以实际上输出还是3.3V,我们不去设置它也行。

图7.6 引脚分配

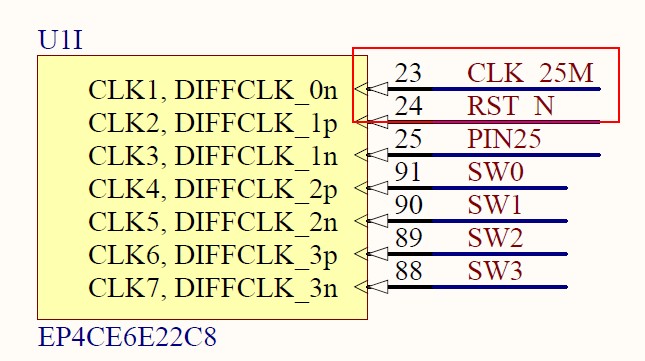

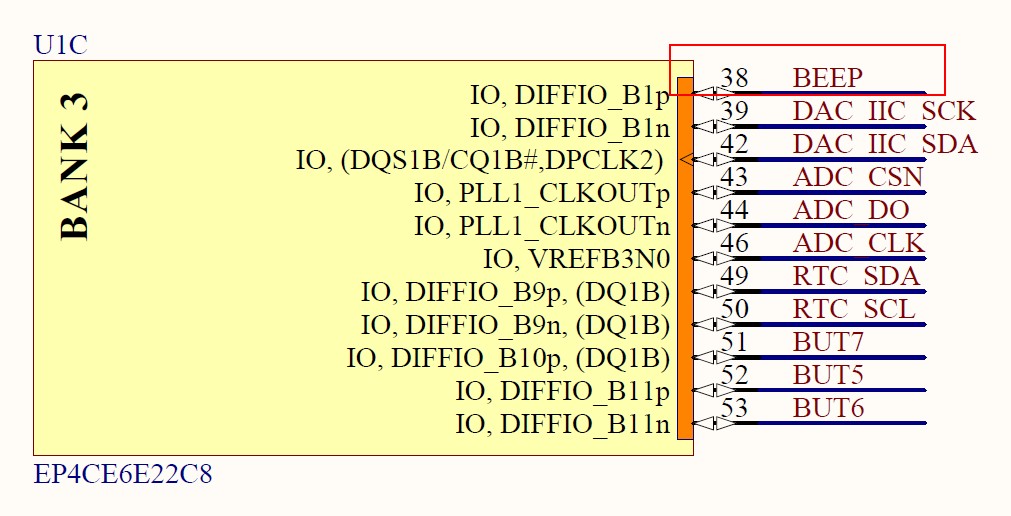

查看SF-CY4开发板的原理图,如图7.7和图7.8所示,这里BEEP对应FPGA引脚号是38,那么前面我们就在Location列输入PIN_38;RST_N和CLK_25M分别为24和23,则输入PIN_24和PIN_23。

图7.7 时钟和复位信号原理图

图7.8 蜂鸣器信号原理图

脚本直接引脚分配

Tcl(Tool Command Language),即工具命令语言。是一种好用易学的编程语言。在EDA工具中广泛使用,几乎所有FPGA开发工具都支持这种语言进行辅助设计。例如这里我们就要尝试用tcl脚本进行FPGA的引脚分配。

前面对ext_clk_25m的引脚分配,我们可以用如下语句实现。

set_location_assignment PIN_23 -to ext_clk_25m

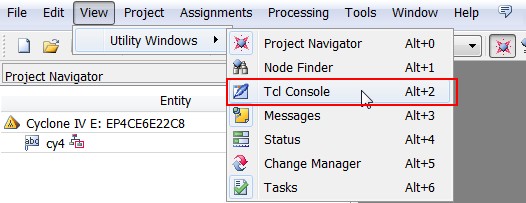

语法“set_location_assignment PIN_A –to B”是固定格式,A代表FPGA引脚号,B代表FPGA内部的信号名称。就这么简单。这个脚本要写到哪里?如图7.9,点击菜单栏“ViewàUtility WindowsàTcl Console”。

图7.9 Tcl Console菜单

接着如图7.10所示,我们在“Tcl Console”中输入以下的3条引脚分配脚本,最后点击“回车”。

图7.10 tcl脚本输入

此时,我们回到“Pin Planner”中,也可以看到所有引脚自动完成分配。