勇敢的芯伴你玩转Altera FPGA连载66:SRAM读写测试

0赞勇敢的芯伴你玩转Altera FPGA连载66:SRAM读写测试

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1i5LMUUD

存储器铺天盖地,并且是各个大小计算机系统(包括嵌入式系统)必不可少的部分。可以毫不夸张的讲,有数据传输处理的地方必定有存储器,不管是CPU内嵌的或外挂的,在做代码存储或程序运行的时候也必定少不了它。而本节的实验对象SRAM(Static RAM)是一种异步传输的易失存储器,它读写传输较快,控制时序也不复杂,因此目前有着非常广泛的应用。

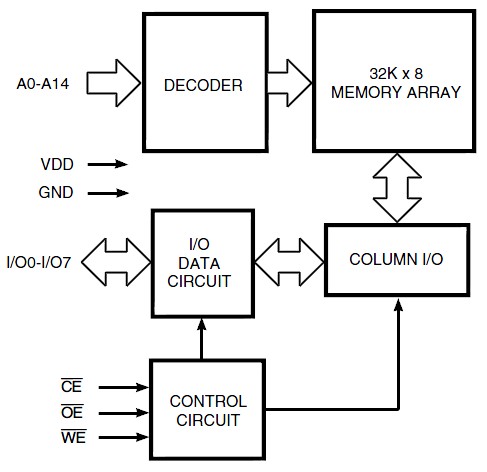

你找来任何一颗SRAM芯片的datasheet,会发现它们的时序操作大同小异,在这里总结一些它们共性的东西,也提一些用Verilog简单的快速操作SRAM的技巧。SRAM内部的结构如图8.34所示,要访问实际的Momory区域,FPGA必须送地址(A0-A14)和控制信号(CE#\OE#\WE#),SRAM内部有与此对应的地址译码(decoder)和控制处理电路(control circuit)。这样,数据总线(I/O0-I/O7)上的数据就可以相应的读或写了。

图8.34 SRAM功能框图

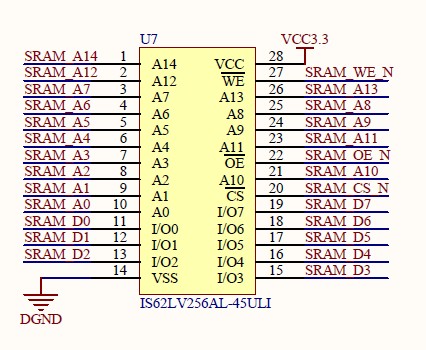

这里就以本实验使用的IS62LV256-45U为例进行说明。其管脚定义如表8.3所示。

表8.3 SRAM接口定义

序号 | 管脚 | 方向 | 描述 |

1 | A0-A14 | Input | 地址总线。 |

2 | CEn | Input | 芯片使能输入,低有效。 |

3 | OEn | Input | 输出使能输入,低有效。 |

4 | WEn | Input | 写使能输入,低有效。 |

5 | I/O0-I/O7 | Inout | 数据输入/输出总线。 |

6 | VCC | Input | 电源。 |

7 | GND | Input | 数字地。 |

本设计的硬件原理图如图8.35所示。

图8.35 SRAM接口

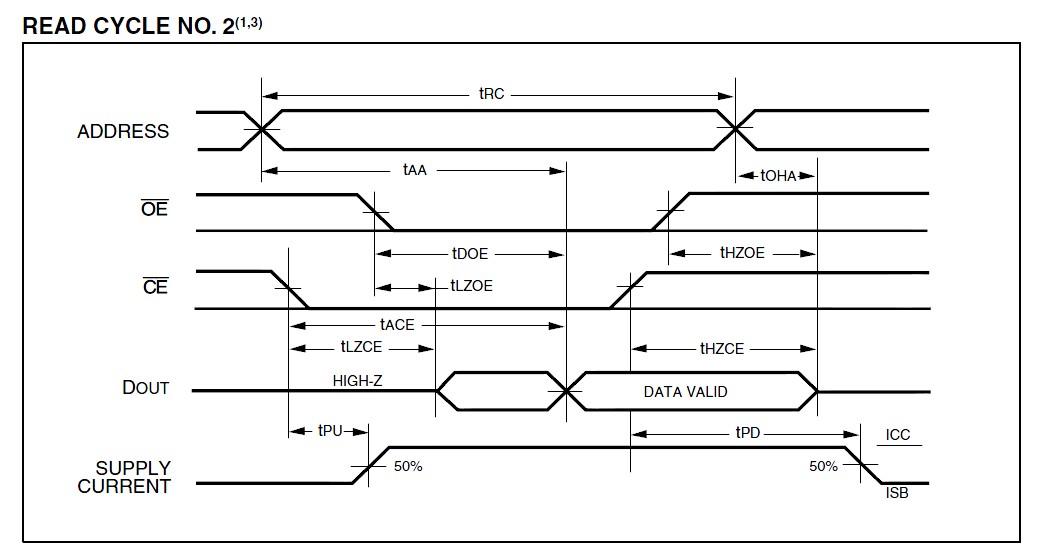

对于SRAM的读操作时序,其波形如图8.36所示。

图8.36 SRAM读时序

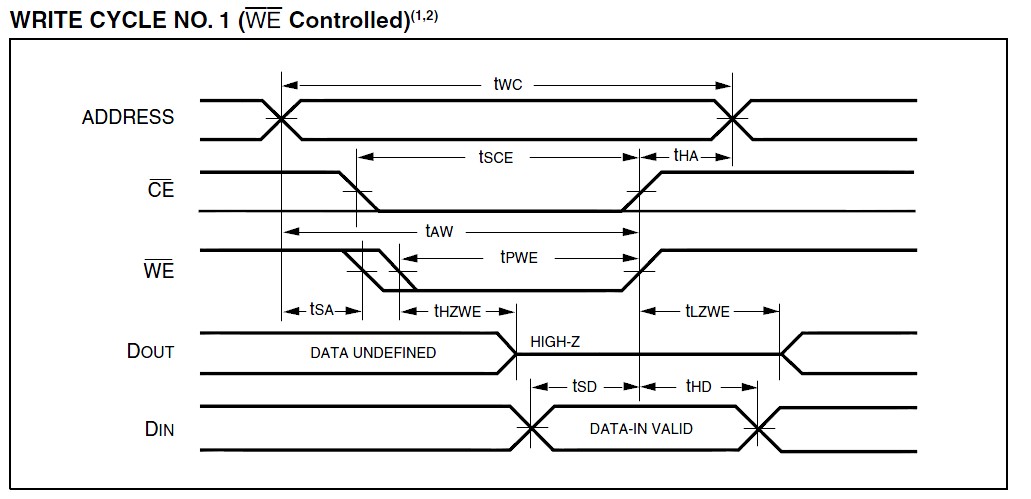

对于SRAM的写操作时序,其波形如图8.37所示。

图8.37 SRAM写时序

具体操作是这样的,要写数据时,(这里是相对于用FPGA操作SRAM而言的,软件读写可能有时间顺序的问题需要注意),比较高效率的操作是送数据和地址,把CE#和WE#拉低。然后延时![]() 时间再把CE#和WE#拉高,这时就把数据写入了相应地址了,就这么简单。读数据就更简单了,只要把需要读出的地址放到SRAM的地址总线上,把CE#和OE#拉低,然后延时

时间再把CE#和WE#拉高,这时就把数据写入了相应地址了,就这么简单。读数据就更简单了,只要把需要读出的地址放到SRAM的地址总线上,把CE#和OE#拉低,然后延时![]() 时间后就可以读出数据了。时序图中列出的相关时间参数如表8.4所示。

时间后就可以读出数据了。时序图中列出的相关时间参数如表8.4所示。

表8.4 SRAM读写时序表

参数 | 定义 | 最小值(ns) | 最大值(ns) |

| 读操作周期时间。 | 70 | — |

| 数据输出保持时间。 | 2 | — |

| 地址访问时间。 | — | 70 |

| 写操作周期时间。 | 70 | — |

| 地址建立时间。 | 0 | — |

| 写结束后地址保持时间。 | 0 | — |

| WEn信号有效脉冲宽度。 | 55 | — |

| 写结束前的数据建立时间。 | 30 | — |

| 写结束后的数据保持时间。 | 0 | — |

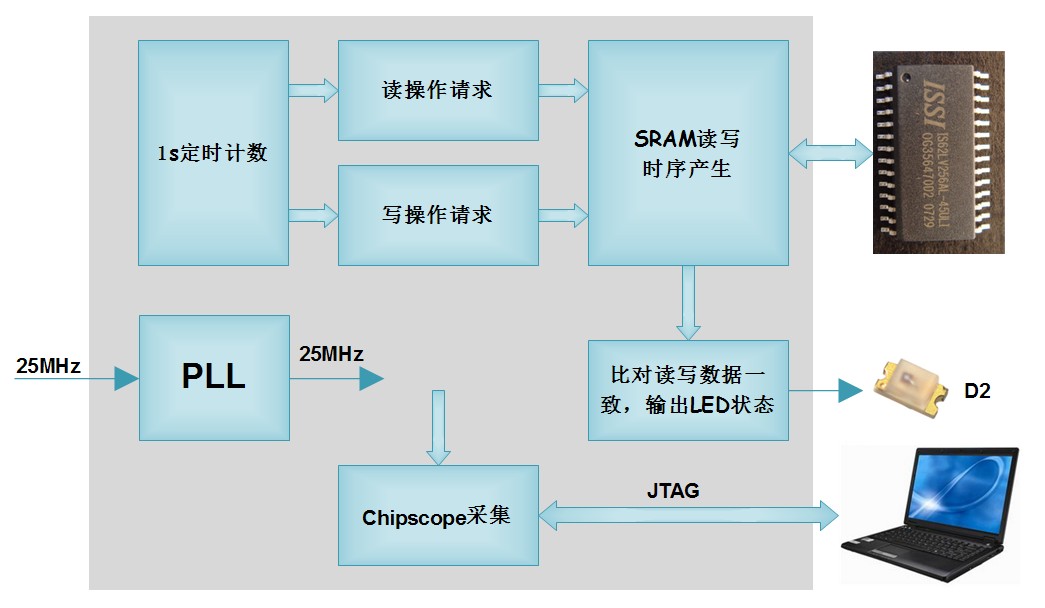

如图8.38所示,本实例每秒钟定时进行一个SRAM地址的读和写操作。读写数据比对后,通过D2 LED状态进行指示。与此同时,也可以通过SignalTap II在Quartus II中查看当前操作的SRAM读写时序。

图8.38 SRAM实例功能框图

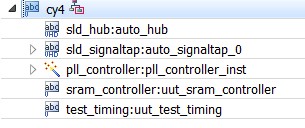

该实例的工程模块划分层次如图8.39所示。

图8.39 SRAM实例模块层次