玩转Zynq连载38——[ex57] Zynq AXI HP总线带宽测试

0赞

1概述

用于PL与DDR3交互的AXI HP总线,它的性能到底如何?吞吐量是否能满足我们的应用?必须4个通道同时使用?还是只使用1个通道?时钟频率的高低对AXI HP总线的带宽有什么影响?这些问题想必是每一个初次使用AXI HP总线的开发者希望评估到的。那么,本实例就搭了一个很基本的架构出来,使用100MHz的AXI HP总线时钟频率(可更改),任意开关每个独立的AXI HP读或写通道,以评估不同通道使用情况下的数据吞吐量。大家可以在此基础上,更改不同的AXI HP总线时钟频率,以评估时钟频率对AXI HP总线的影响。

2 AXI总线协议介绍

参考文档《玩转Zynq-基础篇:AXI总线协议介绍.pdf》。

3 Zynq PS的AXI HP与VIO IP配置

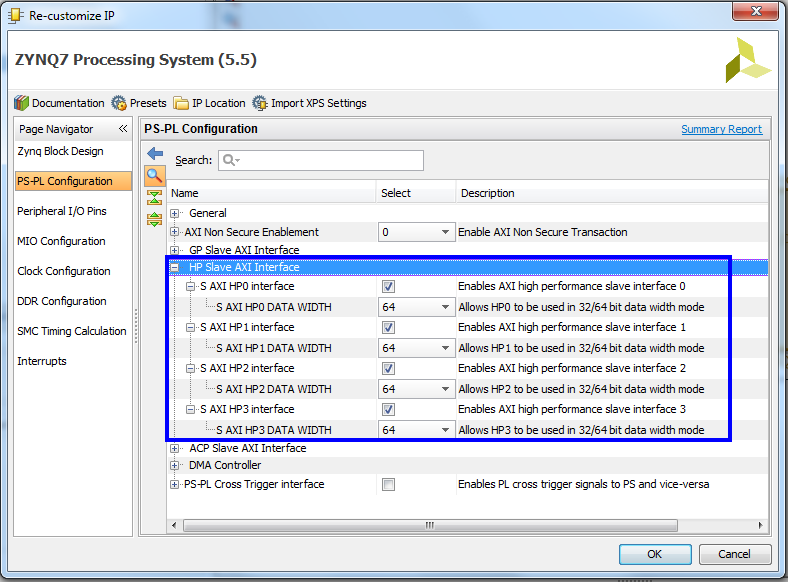

如图所示,在ZYNQ7 Processing System在,点击Page Navigator --> PS-PL Configuration,展开HP Slave AXI Interface,勾选所有的S AXI? interface(?代表0/1/2/3)并选中S AXI HP? DATA WIDTH为64。

在系统框图中,如图所示,将新出现的S_AXI_HP0/S_AXI_HP1/S_AXI_HP2/S_AXI_HP3这4条AXI HP总线,以及它们的时钟AXI_HP0_ACLK/AXI_HP1_ACLK/AXI_HP2_ACLK/AXI_HP3_ACLK接口都引出。

如图所示,在Address Editor页面,默认S_AXI_HP0/S_AXI_HP1/S_AXI_HP2/S_AXI_HP3的地址还未分配,需要点击左侧的图标重新分配地址。

分配好地址后,如图所示。

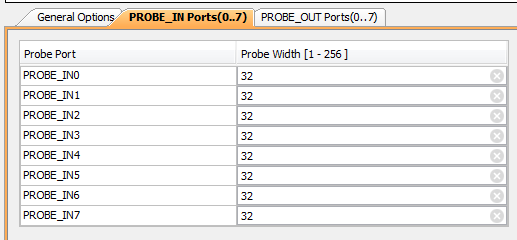

接着,我们需要参考文档《玩转Zynq-工具篇:基于Vivado的Virtual IO在线板级调试.pdf》新增一个VIO IP核,这个VIO IP的配置如图所示。Input Probe Count和Output Probe Count都为8。

PROBE_IN Ports页面8个Port的Width(位宽)都设置为32。

PROBE_OUT Ports页面8个Port的Width(位宽)都设置为1。

在PL代码中,VIO的8个Output Probe将分别用于控制4条HP总线的读通道和写通道的开关;VIO的8个Input Probe将锁存显示对应HP总线读或写通道每秒的数据传输字节数。

4 PL代码解析

工程代码的层次结构如图所示。

zstar.v模块是顶层模块,将ZYNQ Procssing System引出的4条AXI HP总线的读写通道分别连接到各个具体的逻辑模块中。

timer_1s_generation.v模块是1s定时模块,每秒钟定时产生一个脉宽为100个时钟周期的复位信号timer_1s_rst_n,读写模块的带宽以这个复位信号为周期进行计算。

axi_hp0_wr.v模块实现连续数据写入AXI HP总线的写通道。axi_hp0_rd.v模块不断的送AXI HP的读地址。Vio_0.v模块是例化的VIO IP模块,引出各个HP总线的读或写使能开关以及对应通道的带宽。

5嵌入式软件工程创建

参考文档《玩转Zynq-工具篇:导出PS硬件配置和新建SDK工程.pdf》导出PS硬件工程,并打开EDK新建一个HelloWorld的模板工程。本实例并不需要在嵌入式软件中做任何其它的功能实现,只需要在.bit文件烧录完成后,运行嵌入式软件即可(主要是PL端的时钟源是来自Zynq PS,因此必须在嵌入式软件运行起来后,才能够产生时钟信号)。

6板级调试

在Zstar板子上,设置跳线帽P3为JTAG模式,即PIN2-3短接。

连接好串口线(USB线连接PC的USB端口和Zstar板的UART接口)和Xilinx下载线(下载器连接PC的USB端口和Zstar板的JTAG插座)。使用5V电源给板子供电。

参考文档《玩转Zynq-环境篇:XilinxPlatformCableUSB下载器使用指南》烧录PL工程编译产生的.bit和.ltx文件到Zstar板中,如图所示。

参考《玩转Zynq-工具篇:SDK在线运行裸跑程序.pdf》导出硬件并打开EDK,创建HelloWorld模板工程。运行工程,注意PL的.bit文件已经烧录好,不用再次烧录,直接运行.elf文件即可。

回到Vivado,在Hardware Manager界面点击左上角的Refresh device按钮。

双击刷新后出现的hw_vio_1所在行。

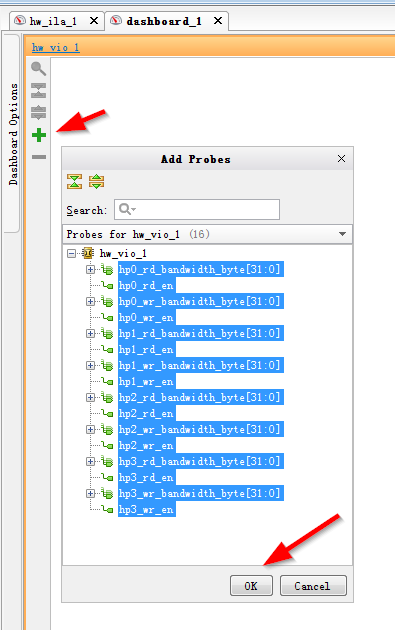

出现的dashboard_1界面中,点击左侧的+号,弹出Add Probes窗口,选中所有VIO信号,点击OK,将它们加入到主界面中进行控制或状态监控。

可以选中所有的Output类型的VIO,右键单击,弹出菜单中选择Toggle Button,后续可以通过点击这些信号来更改1或0的电平状态切换。

同样的,选中所有Input类型的VIO总线信号,单击右键,弹出菜单中展开Radix,点击Unsigned Decimal,即以10进制查看这些总线接口。

接下来,我们就可以通过点击各个en信号,对应的开启某个或某几个AXI HP总线的读或写通道,查看它们的数据吞吐量。如图所示,AXI HP0的读通道开启,吞吐量达到每秒344MByte。

如图所示,AXI HP0的读通道和写通道同时开启,吞吐量分别达到每秒333MByte和556MByte。

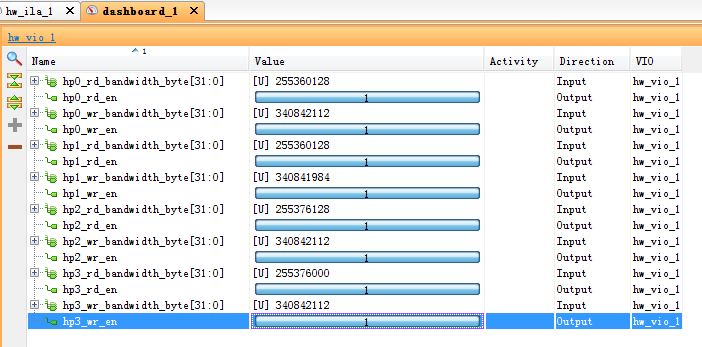

如图所示,所有4条AXI HP总线的读通道和写通道同时开启,每个读通道的吞吐量都在每秒255MByte左右,每个写通道的吞吐量都在每秒340MByte左右。说明4条AXI HP总线的吞吐量其实是对等设计的,在同等时钟频率和访问方式下,它们的吞吐量是相当的。相比于使用更少的AXI HP总线,从测试发现相同条件下的单通道带宽反而降低了。究其原因,很好解释,在更多的AXI HP总线通道(不同DDR3地址块)之间频繁切换所需要的DDR3地址切换开销会越来越大,那么就导致单通道的带宽会有所降低。

更多资料共享

腾讯微云链接:https://share.weiyun.com/5s6bA0s

百度网盘链接:https://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw

提取码:ld9c