【转载】基于Vivado玩耍ZedBoard——自制IP核 + SDK注意事项

0赞硬件平台:ZedBoard

软件平台:vivado2014.2

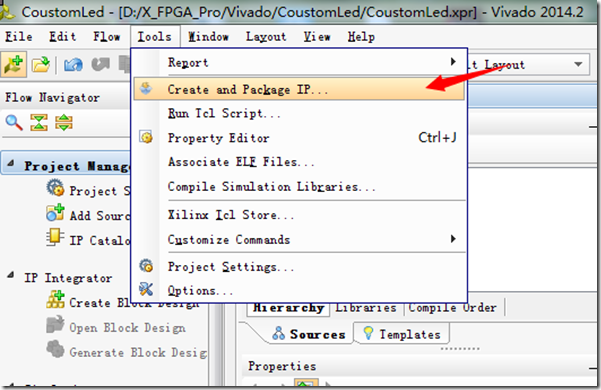

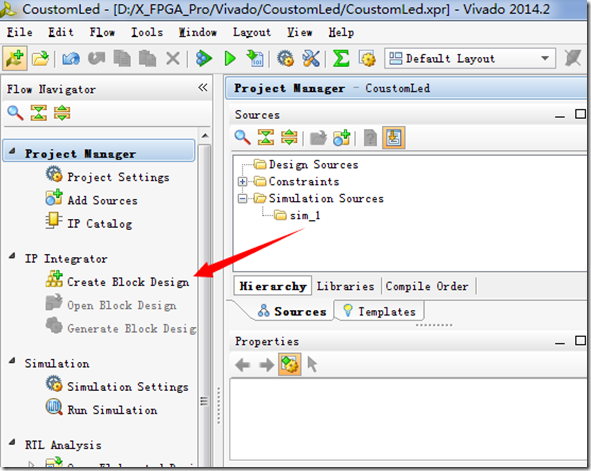

首先新建一个工程之后,出现如下界面~~

next

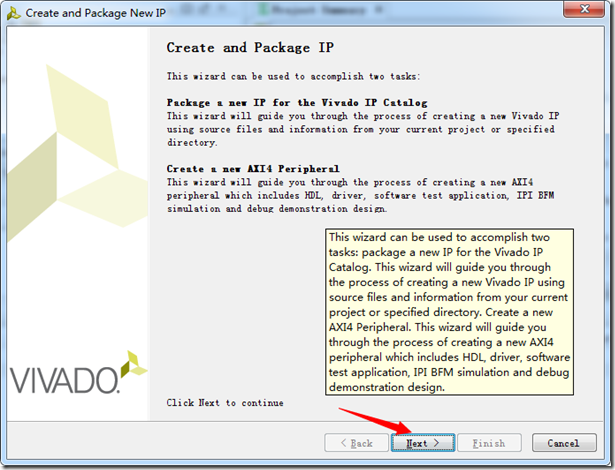

next,创建一个AXI4总线的IP:

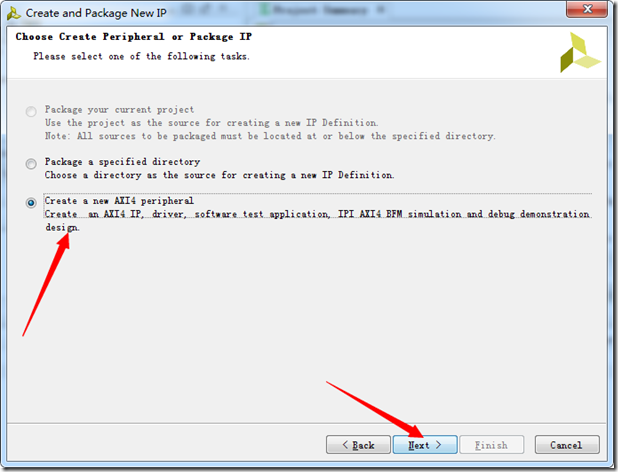

至此,一个AXI4总线的模型的框架就建好了,不过既然是自制,当然是需要加入自己东西咯~~

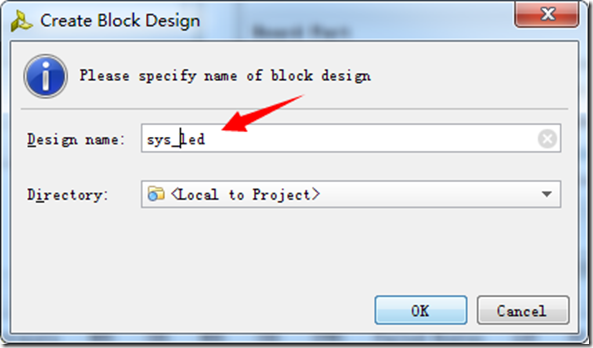

不急,继续,新建一个Block,用来放置IP核们,GO!GO!GO!

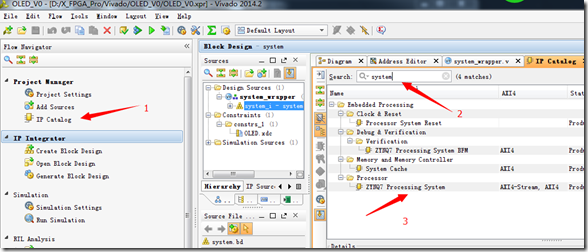

首先添加一个zynq核:

再,双击zynqIP:

告诉大家一个小技巧,如下这样可以为我们的zedboard添加约束,嘿嘿~~

通过同样的方法添加自己的IP:

添加了之后,是时候我我们自己的IP“添油加醋”了:

编辑我的IP

点击OK:(之后会弹出一个新的工程,专门针对IP的)

接下来,我们要修改的就是这两个文件:

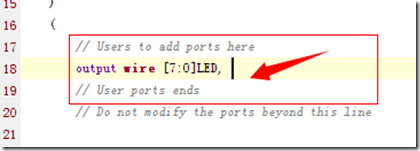

一个个来,先修改第一个:(空都给你留好了了只等,自己去填啊)

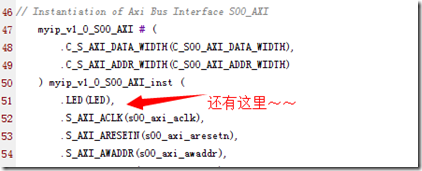

在来修改第二个:

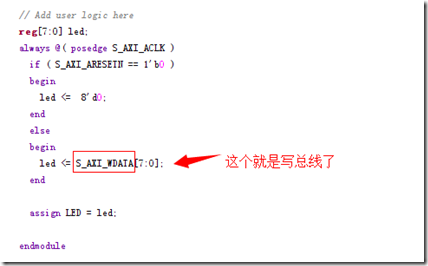

再添加,自己的用户逻辑:

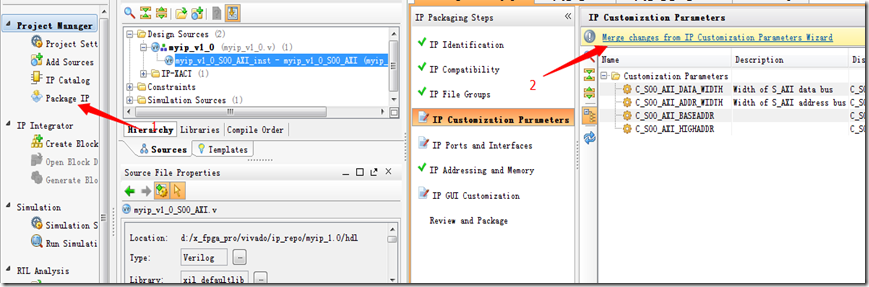

修改结束保存下,接着干:

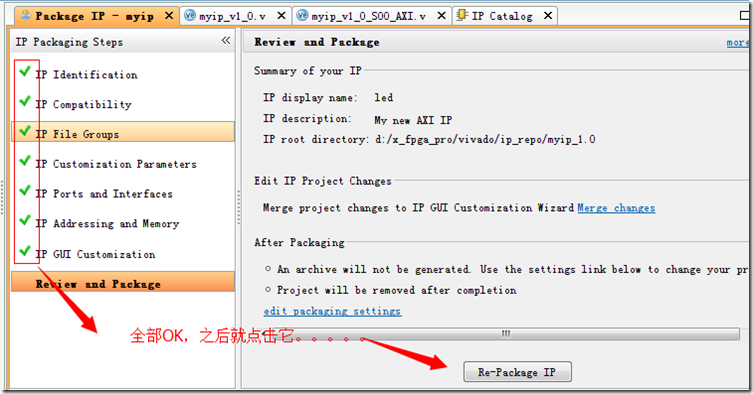

好了,我们的IP编辑完毕了~~

最后 把引脚弄出来,如下~~

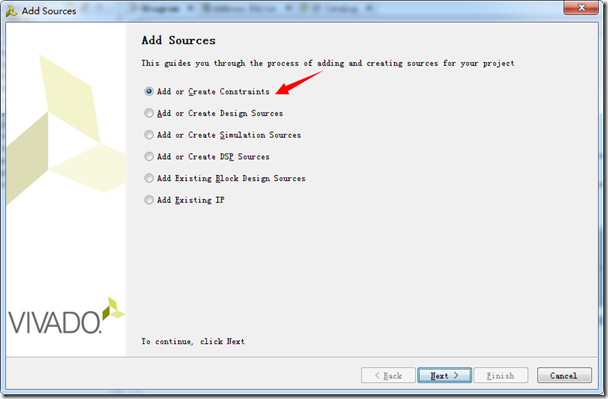

那么接下,为自己IP添加引脚约束,(不用管其他的?只用负责自己的?。。。对,是的哦!)

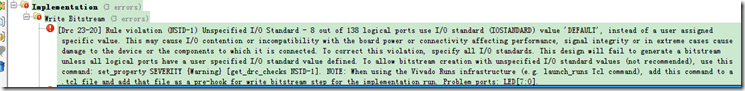

如果不为自己的IP添加引脚约束会如何呢?好吧,我就告诉吧,我悲剧的没有添加的结果(编译好久的好不好==!)

这个是没有分配LED引脚的结果~~

具体,代码我也贴出来吧~~

set_property PACKAGE_PIN T22 [get_ports {LED[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[0]}]

#NET LD0 LOC = T22 | IOSTANDARD=LVCMOS33; # "LD0"

set_property PACKAGE_PIN T21 [get_ports {LED[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[1]}]

#NET LD1 LOC = T21 | IOSTANDARD=LVCMOS33; # "LD1"

set_property PACKAGE_PIN U22 [get_ports {LED[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[2]}]

#NET LD2 LOC = U22 | IOSTANDARD=LVCMOS33; # "LD2"

set_property PACKAGE_PIN U21 [get_ports {LED[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[3]}]

#NET LD3 LOC = U21 | IOSTANDARD=LVCMOS33; # "LD3"

set_property PACKAGE_PIN V22 [get_ports {LED[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[4]}]

#NET LD4 LOC = V22 | IOSTANDARD=LVCMOS33; # "LD4"

set_property IOSTANDARD LVCMOS33 [get_ports {LED[5]}]

set_property PACKAGE_PIN W22 [get_ports {LED[5]}]

#NET LD5 LOC = W22 | IOSTANDARD=LVCMOS33; # "LD5"

set_property PACKAGE_PIN U19 [get_ports {LED[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[6]}]

#NET LD6 LOC = U19 | IOSTANDARD=LVCMOS33; # "LD6"

set_property IOSTANDARD LVCMOS33 [get_ports {LED[7]}]

set_property PACKAGE_PIN U14 [get_ports {LED[7]}]

#NET LD7 LOC = U14 | IOSTANDARD=LVCMOS33; # "LD7"

复制代码

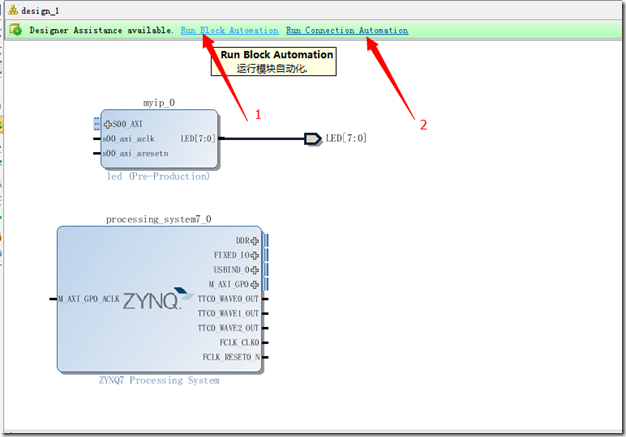

好了IP都添加完了,开始连线吧~~~

好了,点两个确定之后就连接好了:如下

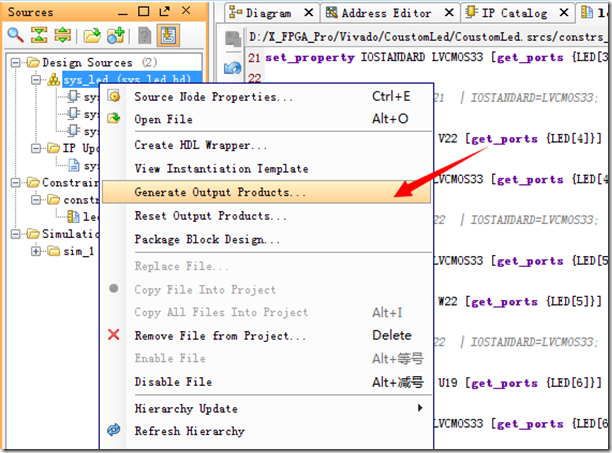

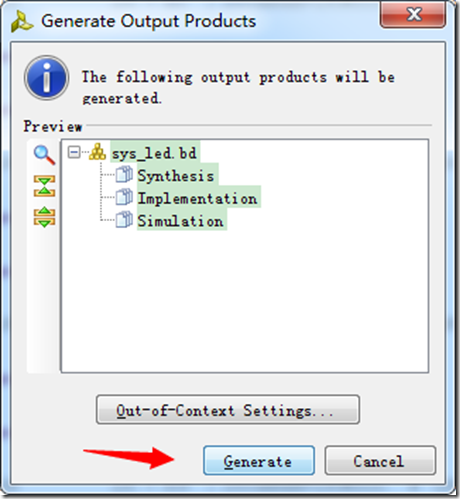

OK还有很重要的一步,接下来Generate Output Products: 这一操作会生成 Block的对应的HDL文件。

最后,为我们的Block创建一个顶层文件:

这么麻烦的事情当然是交给Vivado,让她帮我们,一键搞定:

生成的顶层文件如下:(这时Block之上就出现了顶层文件,话说真是方便啊~~)

好了,可以产生bit文件了:

顺利的话,应该是编译成功啦!

接下了,开始SDK的了,好戏开始了~~(累了就休息会)

//--------------------------------华丽分割线-------------------------------------

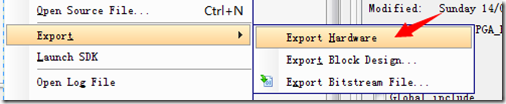

我们继续~~将我们刚刚弄好了硬件信息,导入到SDK,他会为我们产生一些头文件

进入SDK!!

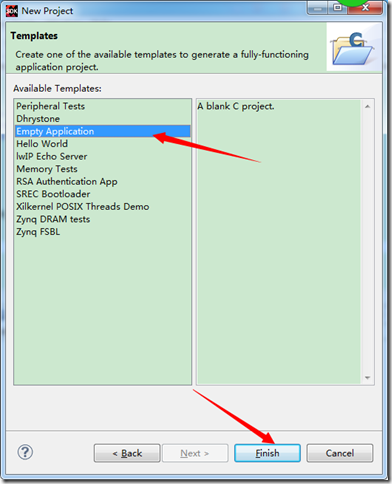

SDK已经打开(打不开?那去看我前一篇博客~~),新建一个工程:

新建一个空的工程,点击Finish

再创建一个C文件:

添加代码如下:

#include

#include "xparameters.h"

#include "xil_io.h"

int main(void)

{

Xil_Out32(XPAR_MYIP_0_S00_AXI_BASEADDR, 0x55);

return 0;

}

复制代码

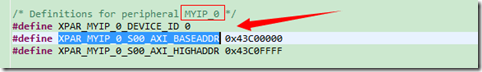

你要问,“XPAR_MYIP_0_S00_AXI_BASEADDR”这个长长的是个啥啊?

我们去"xparameters.h"头文件里看看:(正是我们自己IP的基地址啊)

好了,Ctlr + B,编译一下,(我去,还有一个警告!!)

莫慌~~~右击工程,Clean一下,该警告可除也~~

接下来,就是下载,调试了,上篇博客( [vivado]SDK那些事儿——初试),已经说了,就不再重复了~~

总结:

这次虽说是自定义IP,但是基本和vivado自带的IO IP没什么分别。

当然,这个过程是描述清楚了。自己想添加什么复杂的逻辑,就自己发挥了~~