面向PM-QPSK/QAM相干光通信系统的支持16路并行处理单元数字锁相环的FPGA实现

0赞摘要:基于Inter® Stratix V系列FPGA (速度等级=3)实现支持16路并行处理单元的数字锁相环,支持运行时钟速率>450MHz,该数字锁相环检相器采用Gardner算法,支持PM-QPSK/16QAM/64QAM/128QAM等不同调制方案,单偏振态最大符号速率3.6GBaud(16/2*0.45);占用LE约2W,占用18*18硬核乘法器74个;设计最大修正时钟偏差+/-224ppm;32GBaud-PM-16QAM相干离线实验数据验证了该FPGA实现的有效性,FEC=3.8e-3处硬件实现代价Q<0.1dB。

1 数字锁相环原理部分

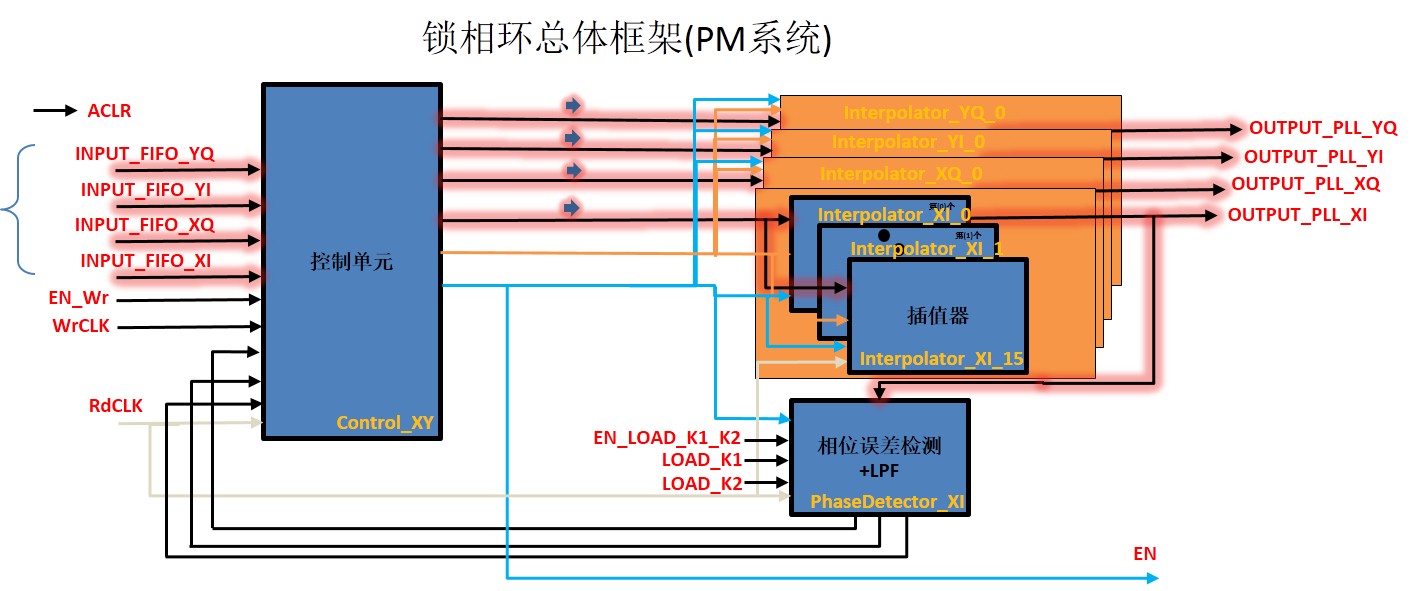

Fig. 1 基于16路并处处理单元数字锁相环的FPGA实现 (Inter® Stratix V系列FPGA 速度等级=3; 支持时钟速率>450MHz) 支持PM-QPSK/16QAM/64QAM/128QAM等不同调制方案。

数字锁相环原理如图1所示,INPUT_FIFO_XI/XQ/YI/YQ分别为来自X和Y偏振态的四路信号输入(XI/XQ/YI/YQ),分别由16路并行构成(同时输入连续的16个采样点 基于2Sa/符号);经过插值器后输出;相位误差检测器由Gardner算法实现,算法中的K1和K2系数控制收敛速度,可通过外部控制并赋值。该算法方案面向短距离<800km而设计,长距离PDM、CD等降低锁相环锁定能力,需要其他算法。

2 逻辑资源占用情况

Fig. 2 逻辑资源开销一览(综合后)

锁相环部分占用逻辑资源2W;占用18*18硬核乘法器74个;如上图2所示。

3. 32GBaud-PM-16QAM离线实验数据分析

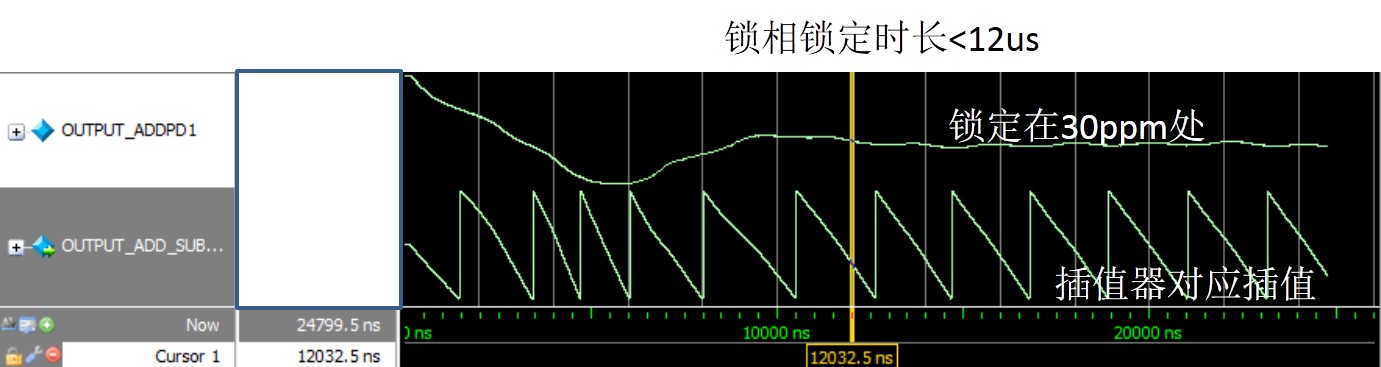

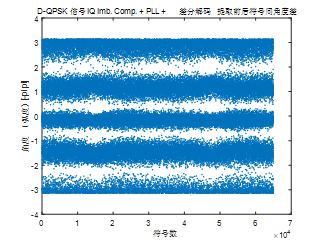

Fig 3. 32GBaud-PM-16QAM对应OSNR=18dB、+30ppm、FEC limit附近收敛情况,收敛过程中Gardner系数K1和K2固定没有改变

4. 2.5GBaud-SP-QPSK实时实验数据分析

第一版实时测试平台

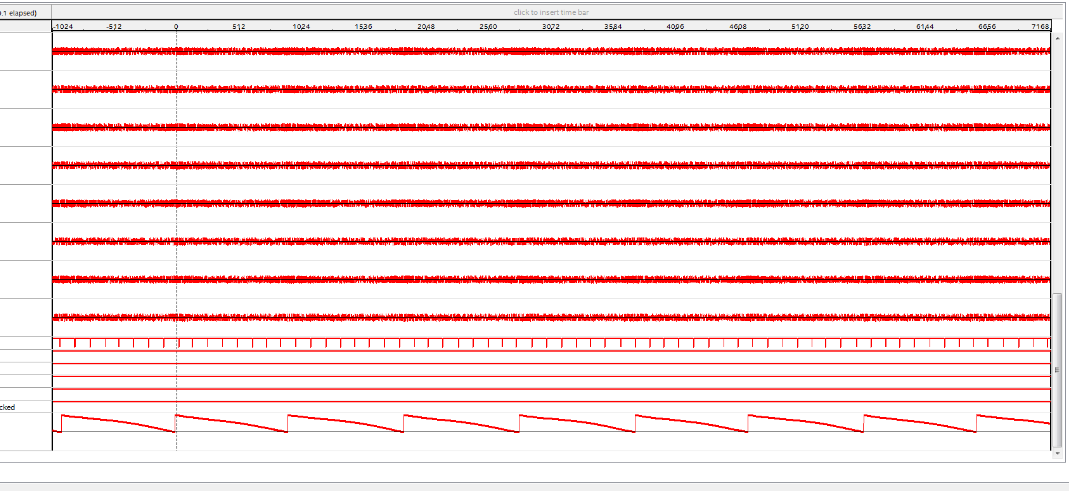

Fig 4. 实时SP-QPSK系统中基于gardener的16路并行处理全数字锁相环实现锁定

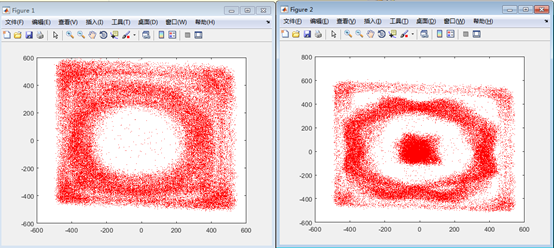

图5. 实时PLL锁定后输出基数和偶数采样点(左为最佳采样点,右图非最佳采样点)

Fig. 6. 实时SP-QPSK差分解调后星座图

更新中。。。(最后更新自2018年6月7日)

jucheng719@qdu.edu.cn