基于40Gbps速率DQPSK调制光自相干探测技术的空间激光通信接收机

0赞激光通信因其速度高、保密定向等优势成为取代/提升微波通信的下一代通信技术。激光通信可实现卫星与卫星间、卫星与地面间、卫星与战机间、以及岛屿与陆地间高速大容量信息传输及组网。光自相干探测技术是实现星地激光通信重要的可行方案。

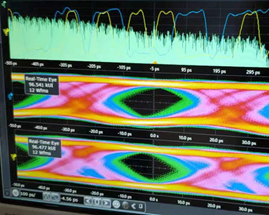

Fig. 1 (左) 40Gbps速率DQPSK调制光自相干探测接收机前端电路;(右) 40Gbps速率光背靠背测试眼图。

公司研发的40Gbps速率光DQPSK调制自相干探测接收机前端电路及B2B下眼图如图1所示。重要指标如下

a. 功耗:~5W

b. BER=1e-3时接收机灵敏度:-32dBm (W/ EDFA)

c. 0.5dB接收机灵敏度代价时多普勒频移跟踪能力:0.07GHz/s

d. 接收前端算法基于FPGA Verilog实现,方便移植,逻辑资源消耗10K (Cyclone IV)

e. 系统仅仅需要1个激光器

f. 冷启动时间<45s(第一次启动/外界温度变化剧烈);热启动时间<8s(外界温度等变化较小)

f. 光接收前端电路与核心FPGA间采用SPI接口控制

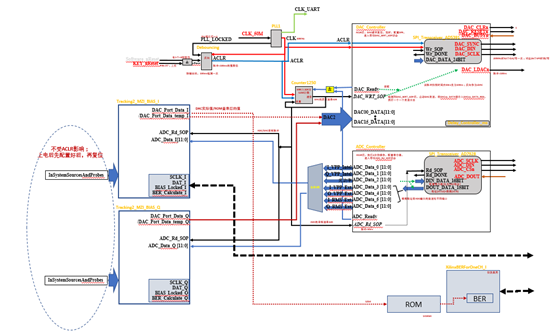

Fig. 2 基于FPGA实现的自相干光DQPSK解调器偏置点最优搜索和实时跟踪方案。

Cyclone IV芯片实现的功能如图2所示,主要负责ADC/DAC时序控制、偏置点搜索及跟踪算法等。

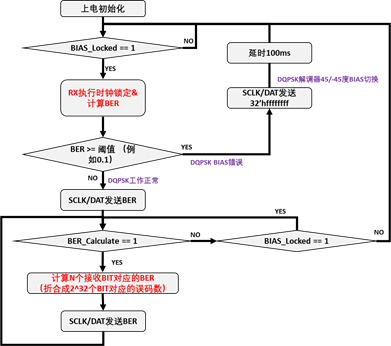

Fig. 3 光自相干接收前端电路与高性能FPGA间通信机制控制。

Cyclone IV芯片与Xilinx等高性能FPGA间通信控制机制如图3所示。

公司可提供硬件电路、FPGA侧软件代码及进一步的研发服务。

青岛相干光通信技术有限公司

联系方式: +86 16678693710

Space laser communication receiver based on 40Gbps rate DQPSK modulation optical self-coherent detection technology

Laser communication has become the next generation communication technology to replace/improve microwave communication because of its advantages such as high speed, confidentiality and orientation. Laser communication can realize high-speed and high-capacity information transmission and networking between satellites, between satellites and the ground, between satellites and fighters, and between islands and land. Optical self-coherent detection technology is an important and feasible scheme to realize satellite ground laser communication.

Fig. 1 (left) Optical front end circuit of 40Gbps rate DQPSK modulated optical self-coherent detection receiver; (right) 40Gbps optical back-to-back test eye diagram.

The front-end circuit and B2B lower eye diagram of 40Gbps rate optical DQPSK modulation self-coherent detection receiver developed by the company are shown in Fig 1. Important indicators are as follows:

a. Power consumption: ~ 5W

b. Receiver sensitivity when BER = 1e-3: - 32dBm (w / EDFA)

c. Doppler frequency shift tracking capability at sensitivity cost of 0.5dB receiver: 0.07Ghz/s

d. The receiving front-end algorithm is implemented based on FPGA Verilog, which is convenient for transplantation and consumes 10K logic resources (cyclone IV)

e. The system only needs one laser

f. Cold start time < 45s (first start / drastic change in external temperature); Hot start time < 8s (small change in external temperature)

f. SPI interface control is adopted between the front-end circuit of optical receiving and the core FPGA.

Fig. 2 Optimal search and real-time tracking scheme of bias point of self-coherent optical DQPSK demodulator based on FPGA.

The functions realized by cyclone IV are shown in Fig 2. It is mainly responsible for ADC / DAC timing control, offset point search and tracking algorithm.

Fig. 3 Communication mechanism controller between optical self-coherent receiving front-end circuit and high-performance FPGA.

The communication control mechanism between cyclone IV and Xilinx/other high-performance FPGAs is shown in Fig 3.

The company can provide hardware circuit, FPGA side software code and further R&D services.

Tel.: +86 16678693710

Email:jucheng719@qdu.edu.cn