【转】FPGA三国志-第三篇/SOPC篇3-1

0赞

PLD的重新定义PLD是什么,Programmable Logic Device. 当然今天应该换个称呼了:Processor+ Logic+DSP了,世界就是这样不停的变化来维持他的稳定。

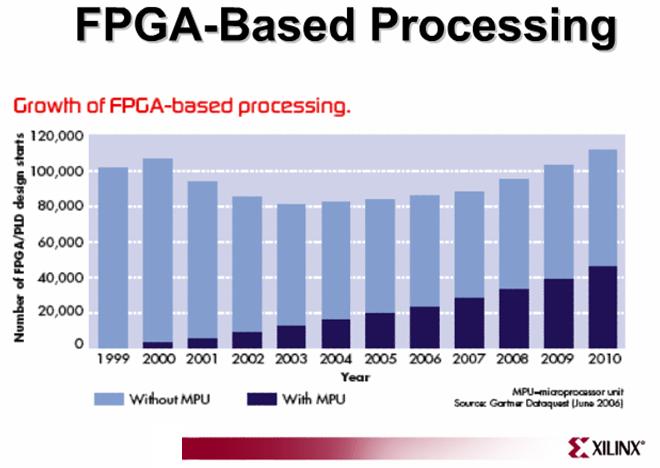

表1列出了Altera®可编程解决方案的主要历史创新发展过程。,可以看到在2000年的时候,FPGA的厂商已经开始在嵌入式微处理器方面开始崭露头脚。 当然起初引来的也有一片哗然。 说效率低下,难以开发。 新鲜事物的诞生总是要经过这样的阵痛期。

在2002年,就有众多厂家出来声称都支持嵌入式软核CPU。 甚至也和当时流行的8051 turbo以及一些ARM进行比较。

处理器嵌入在FPGA中,需要什么样的温床?

的确,在推出Nios soft processor 两年之后,在我们周边也开始陆续有开始吃螃蟹的了。 但是,还是回到结构的老话题上,来谈论一下为什么这个时候出现了由FPGA制造商推出的CPU,实际上在1997年,就已经有什么FPGACPU的说法甚嚣尘上。 而且也有人在Xilinx和Altera上面分别实现了原形。

开始在FPGA嵌入大块RAM的时候,很多人抨击这种结构,只是一个动物园里面的老虎,实际上就是和猫差不多的杀伤力。 不可以否认,它不如分布式RAM来的灵活,但是它可以作为一些Cache,或者是紧耦合的RAM,还有就是它的规模在容量增加的时候,仍旧有很好的速度,那就可以作为CPU的Cache了。 Altera的RAM都是做在同一列的,很方便级联。 另外总线宽度也很容易更改。

还有就是CPU里面总是有很多总线,内部总线。 由于丰富的行联线的存在,在几列行资源里,就可以轻松集成RAM,CPU要的逻辑资源,以及总线的结构。 这样,CPU也就顺利的在FPGA的世界里粉墨登场了。 虽然起初只是16bit的。

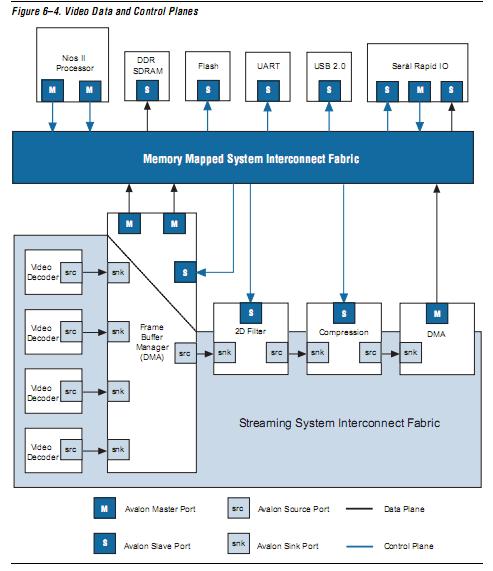

2002年,Altera的开发软件已经趋于稳定,可以说已经很适合自己产品的结构,而且布线效率非常高。同时Altera的Nios也上升为NiosII,这个时候NiosII已经蜕变为美丽蝴蝶---一个32bit的RISC CPU。 而且Altera又采用了非对称的机构实现了革命性的Avlon互联体系。 关于这个体系的由非对称可以覆盖对称的,或不对称性的应用,我们以后详细聊。 总而言之。 如果再有一款更好结构的低成本的FPGA,那无异于在FPGA市场上刮起一场飓风!

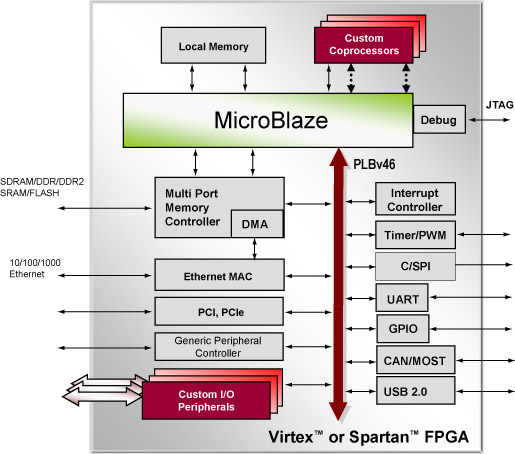

Xilinx有Microblaze,其他的有ARM的核,实际上FPGA上实现的CPU,不是由一个CPU的内核来决定他的应用,而是谁有最好的互联体系,能和外围设备,和FPGA中的RAM,乘法器,以及其他定制逻辑更好桥接,粘合成一个SOPC,那才是真正意思上的软核。 那究竟什么样子才好呢?

- 可以增加多个核来弥补自己速度上的缺陷,提高更多的并行处理

- 灵活的总线结构,可以连接高速,慢速,master,salve的模块

- 可以将客制化的逻辑,有效集成到CPU的指令体系。

- 有面向不同应用,可以进行裁剪的CPU core

- 方便片上调试的环境

- 可以快速自动实现外设资源冲突仲裁的机制

- 可以实现以软代硬,或者以硬代软,在软硬间转化速度与资源的偏重

如果有以上的特性,那相信留给设计者的只有是无限的遐想空间。

FPGA上的CPU,有太多的元素,你知道吗?

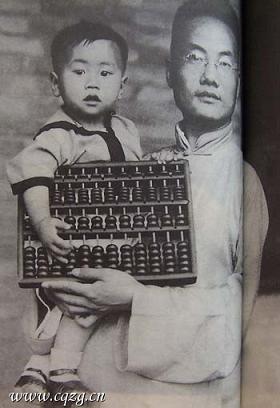

我们从哪里开始讲呢,准备从算盘开始讲CPU,很多人说,我是不是太无聊了呢?听我明天说给你听!看似简单的算盘,绝对孕育着无比的大智慧。 看是简单的Avalon,也同样有很多玄机。 那就是变变变。

来自Xilinx的消息,关于CPU在FPGA设计中的一些预测

神奇的算盘

上回说到算盘。 实际上大家应该都见过这个了不起的发明,只是他出现在你的记忆中的次数越来越少,就忘记了,实际上,很多伟大之处在很早就有历史可以证明的。 看看你平时见到的算盘。

算盘的妙处和Altera的LE排列布局非常相似,或许是巧合吧。

但是这里的偶然也有些必然。 或许我们有一天说,FPGA的结构最早是源于我国的。 哈哈,玩笑啊。

-

可以增加多个核来弥补自己速度上的缺陷,提高更多的并行处理

一个算盘是算盘,级联起来还是算盘,可以横向,也可以纵向 -

灵活的总线结构,可以连接高速,慢速,master,salve的模块

算盘是平行也是并行结构,上面的有两个珠子,下面5个,2也可以代表10,5也可以代表10,同时,进位时也可以暂时存储在高档位,也可以留在本档。进位链和Altera LE的进位布局也是一样。

看一个更久的照片,当然这个也可以代表Cyclone的layout了。

Avalon的奥秘

总线结构:

全交叉,部分交叉型(适合FPGA中的嵌入总线!)

Xilinx的是共享总线型。仍旧属于传统型设计,只是将其搬移到了FPGA中。

处理器接口主要抽象为:

- 共享寄存器

- RAMs

- FIFOs

上面看起来,这两个softcore都差不多,看了下面的特点,你就有答案了。

Selecting Hardware Architecture

Bus

- achieve relatively high clock frequencies

- expense of little

- no concurrency

- common arbitration unit.

- all masters compete for access to

Full Crossbar Switch-NiosII Avalon

- concurrent transactions

- flexible

- high throughput

- large multiplexers

- more masters and slaves are added

- avoid large crossbar switches

Partial Crossbar Switch--Avalon is okey

- connectivity to a subset of the slaves

- provides the optimal connectivity

- operates at higher clock frequencies

- interconnect fabric consumes fewer resources.

- ideal for ASIC or

- FPGA interconnect structures

- slave side arbitration.

Streaming-Avalon Streaming Map

- high speed data transfers

- point-to-point connections between source and sink

- eliminating arbitration

Dynamic Bus Sizing

Understanding Concurrency

Create Multiple Masters

- General purpose processors, such as Nios II

- DMA engines

- Communication interfaces, such as PCI Express

Create Separate Datapaths

Use DMA Engines

- data width

- clock frequency

- more DMA engines

Include Multiple Master or Slave Ports

- increases the concurrency

Create Separate Sub-Systems

Increasing Transfer Throughput

increasing the transfer efficienc

lower frequency devices can be used

Using Pipelined Transfers

- Maximum Pending Reads

- Selecting the Maximum Pending Reads Value

Pipelined Read Masters

Increasing System Frequency

strategy

- introduce bridges to reduce the amount of logic

- increase the clock frequency.

Tatic

Use Pipeline Bridges

- Master-to-Slave Pipelining

- Slave-to-Master Pipelining

- waitrequest Pipelining

Use a Clock Crossing Bridge

Consequences of Using Bridges

- Increased Latency

- Limited Concurrency

- Address Space Translation

Reducing Logic Utilization

Reducing Power Utilization

Reduce Clock Speeds of Non-Critical Logic

Clock Crossing Bridge

Avalon-MM master ports operating at a higher frequency to slave ports running a a lower frequency

- PIOs

- UARTs (JTAG or RS-232)

- System identification (SysID)

- Timers

- PLL (instantiated within SOPC Builder)

- Serial peripheral interface (SPI)

- EPCS controller

- Tristate bridge and the components connected to the bridge