差分ADC-ads1274调试记录

0赞

发表于 2016/12/6 下午6:39:06

阅读(5893)

芯片:ADS1274 (http://www.ti.com/product/ads1274)

供电:AVDD-5V,DVDD-1.8V,IOVDD-3.3V

时钟:CLK=20Mhz(stop-clock),SCLK=10Mhz(stop-clock)

模式:SPI接口,High-Speed-MODE,Discrete输出

输入:-1V~2.5V单端信号经过差分运放转换

下面根据调试问题逐个分析:

1、读出的数据随机,没有任何规律;

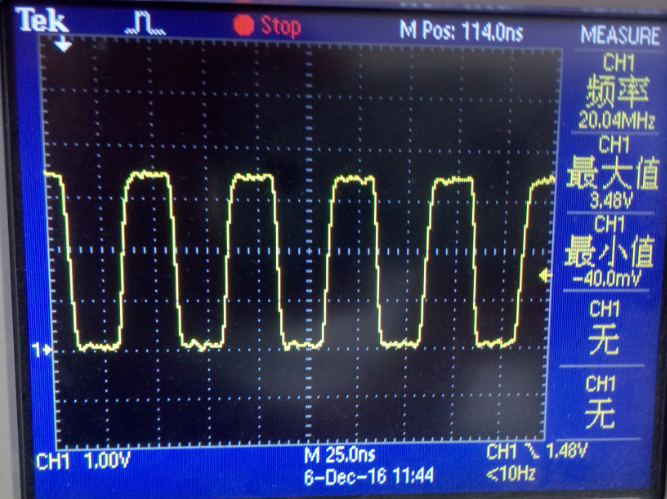

在排查电源时钟等外部环境时,发现时钟信号有较大的上下过冲。

而根据page26对CLK的要求:high-quality, low-jitter;给采样模块用的时钟要clean。

CLK是fpga送出来的,进过3块板子2个连接器,走线比较长,有一定插损,同时上面还挂了个led!

所以把LED去掉,末端电阻从0欧姆换成100欧姆。整个信号变好了,读出的数据跟输入值也对上了。

同时SCLK的信号也要调好。

2、读出值是被测值的两倍

spi接口出来的串行数据经过向高移位得到24bit的测量数据,如果数据相差一倍的话很可能是移位过头了。

page30:MSB data are valid DRDY goes low, Subsequent bits are shifted out with each falling edge of SCLK。在ready信号变低后,最高位就输出了,然后在每个SCLK的下降沿,剩下的bit位依次输出。写逻辑在每个rising-edge采样,共24次,数据就对了。

3、