vivado疑惑解惑零碎知识点

0赞1. vivado中 这个ILA 和VIO 有什么区别呢:

ILA是逻辑分析仪,看芯片内数据波形的

VIO是模拟输入输出口

也就是看信号用ILA ,需要一个触发信号用vio

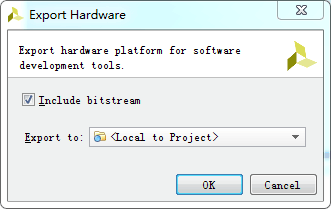

2. vivado中导出硬件理解:

.

导出硬件到SDK ,SDK上用到的资源和外设必须在导出之前要声明和连接到,如果导出硬件之后,SDK 想要用到别的外设,是不是重新回到vivado中重新添加外设,再导出,也就是说所谓的导出来的硬件可以理 解为SDK硬件设备的导出硬件配置信息。

相当于一个积木,你使能了哪些模块,导出后,在sdk里面才能用哪些模块

3. AXI4 STREAM DATA FIFO是输入输出接口均为AXIS接口的数据缓存器,和其他fifo一样是先进先出形式。可以在跨时钟域的应用中用于数据缓冲,避免亚稳态出现。支持数据的分割和数据拼接。在使用该IP核之前,我们应该熟悉该IP核的各种参数设定的含义。

http://blog.csdn.net/qq_20748649/article/details/50265141

4. AXI 总线与ZYNQ 的关系

AXI(Advanced eXtensible Interface)本是由ARM 公司提出的一种总线协议,Xilinx从6 系列的FPGA 开始对AXI 总线提供支持,此时AXI 已经发展到了AXI4 这个版本,所以当你用到Xilinx 的软件的时候看到的都是 “AIX4”的IP,如Vivado 打包一个AXI IP的时候,看到的都是Create a new AXI4 peripheral。到了ZYNQ 就更不必说了,AXI 总线更是应用广泛,双击查看ZYNQ 的IP 核的内部配置,随处可见AXI 的身影。

5. AXI 总线和AXI 接口以及AXI 协议

总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由由数据线、地址线、控制线等构成。接口是一种连接标准,又常常被称之为物理接口。协议就是传输数据的规则。

6. AXI 总线概述

在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线分别为:

AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输;

AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。

AXI4-Stream:(For high-speed streaming data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

7. AXI 接口介绍

三种AXI接口分别是:

AXI-GP接口(4个):是通用的AXI接口,包括两个32位主设备接口和两个32位从设备接口,用过改接口可以访问PS中的片内外设。

AXI-HP接口(4个):是高性能/带宽的标准的接口,PL模块作为主设备连接(从下图中箭头可以看出)。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)

AXI-ACP接口(1个):是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。

8. 每个接口用在什么情况下:

由于减弱了数据传输过程中对于地址的依赖性,AXI4-Stream接口可根据首地址完成系统设备之间大量连续数据的高速传输,适用于图像采集、处理与传输系统;AXI4-Lite是一种低速的数据传输接口,主要用于系统与外设之间的控制或者寄存器信息的交流。

9. DMA 图

![(}1$GTV%N]PVKIX65MKGS@2.png (}1$GTV%N]PVKIX65MKGS@2.png](http://files.chinaaet.com/images/blog/2019/20170402/1000019370-6362676922645508641325353.png)

AXI Direct Memory Access (AXI DMA), 从名字我们知道为带AXI 总线的直接存储通道。其优点是通过PS端的简单配置,就实现PL和DDR3之间的快速存储。 使用AXI_DMA IP时,必然还要添加上zqny system 核,若涉及中断使用,可以使能两个PL-PS间的中断IO。在初步建立DMA的M2S和S2M循环链路时,可以添加外部如FIFO buf,作为实验用途。

另外在http://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html处,有个比较简单的例程,也比较适合学习。也后续再写blog说明。

DMA IP 中,需要关注的就是M_AXIS_MM2S、S_AXIS_S2MM、mm2s_introut、s2mm_introut四个iOS 其它系统自动连线。M_AXIS_MM2S、S_AXIS_S2MM为数据流总线,mm2s_introut、s2mm_introut为中断信号,可连接到PS端,在PS端编程控制处理。其中MM2S为DDR3 到 PL, S2MM为PL到DDR3。

其和DDR3单独PS端读写区别为,DMA可以大数据量的批量处理,效率要远高于单地址的数据读存。

10. 外设接口:

这些外设接口不仅可以通过MI0(MultiuseI/0)从处理器系统部分引出,也可以通过EMIO(Extendable Multiuse I/O)从可编程逻辑部分引出,这种结构极大的増加了系统外设接口的数量,也给系统的设计和实现带来了很大的灵活性。

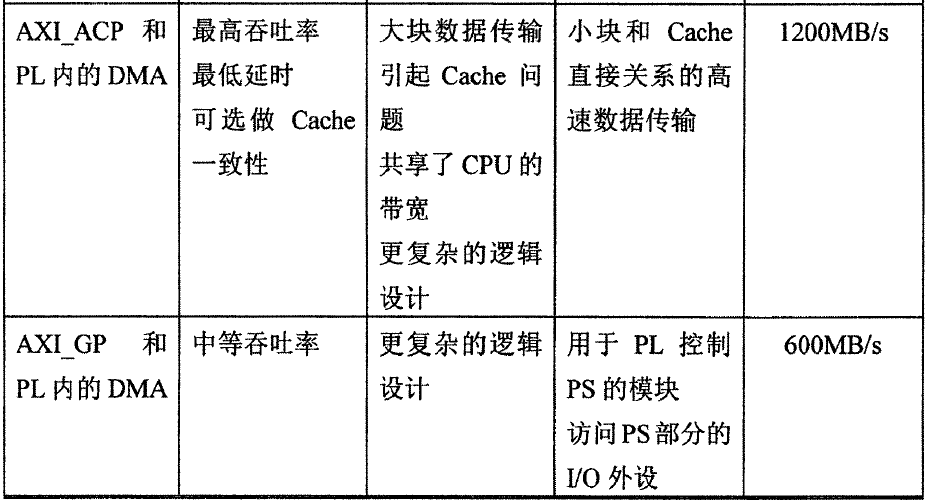

11. 接口部分的性能和引用参照表

![FF[RK9LA8A2]8SW~3JFZ]7Q.png](http://files.chinaaet.com/images/blog/2019/20170403/1000019370-6362682970416298734475507.png)