基于FPGA的位同步时钟提取电路设计及M序列生成器

0赞

发表于 7/30/2016 11:57:57 AM

阅读(8525)

这个设计是最近几天的湖北省2016年电子设计“TI杯“的题目F题,最后一次机会参加电赛了,去年国赛,选做频率计,当时FPGA没学好,初生牛犊不怕虎,谁知道却遇到了跨时钟域的亚稳态,当时菜鸟一枚,没能解决,后来才知道自己当时离成功只有一步之遥,只要搞个握手的通机制就好,亚稳态就可以解决了,后来实在压抑不住,再拿出器件测试,确实如我所想,WORK了,伤心的吧嗒聊!

今年苦学了一年的FPGA,对其有了更加深入的掌握,选F题,经过几个通宵,把题目中设计的FPGA的部分都做好了,经过仿真验证,调试,板级验证,很好的完成了题目要求。殊不知,由于M序列信号源没有低通滤波器!专家直接不让测后端,那个我做了不错的部分,也是分值能决定成败的部分,不让测了,实乃失望至极!

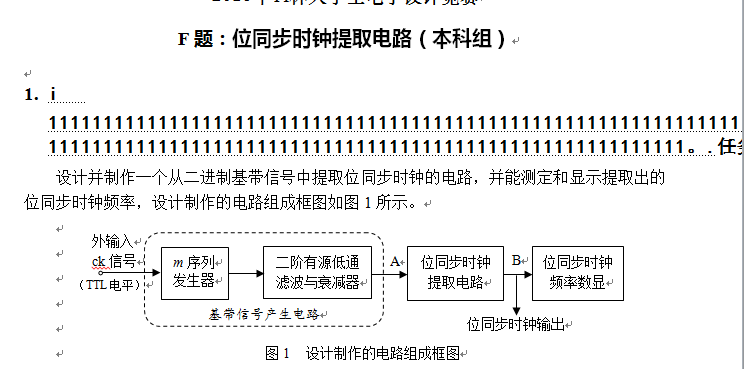

进入正题,位同步时钟同步信号的提取的重要性,我就不多说的,读者请查阅相关参考资料。这个设计主要的框图如下:

我把赛题设计FPGA的部分的完整版放在附件,包括相关代码,读者有兴趣或者又需要,可以参考一下。如图所示,专家只让我测了由FPGA产生的M序列发生器,由于没有做起中低通滤波器,所以后面的部分统统都不让测了,那部分的分值才是最高的,也是我做的最好的部分了。

我所采用的方案全部都是基于FPGA包括M序列部分和位同步时钟提取电路。基于他们的特点,前者用的Verilog,后者参考期刊论文的成果,用的VHDL编写并且有所补充。两部分分别在两快FPGA板子上实现了。时间原因,我把相关资料全部压缩作为附件,读者可查阅!

附件:百度云盘链接:http://pan.baidu.com/s/1o80D8MY 密码:4ahk