能给个安全点的fifo吗

0赞

发表于 2013/8/13 下午6:21:51

阅读(3884)

调试一个基于altera FPGA的项目,发现开机200次,就会有1到2次的开机不正常现象,但只要是成功开机了,无论运行多久都是正常的。

遇到这类问题,按照经验来说 一般首先想到的可能是电源硬件出了问题,是否负载突变,负载过重了,但是用示波器看了几天的电源波形,都没有看出任何端倪来。

开机后,所有的逻辑都在FPGA里运行,如果不是电源问题,那很大的可能就出在FPGA上了。因为绝大部分的情况下运行都是正常,如果逻辑有差错,每次开机都会出问题,所以内部的逻辑应该是没有问题的。FPGA外围有许多外设,只要存在外设和FPGA的连接,就可能出现时序约束不满足的情况,利用时序分析工具,将外设查了个遍,也没有任何问题。

最后又回到曾今怀疑过的复位问题上,因为现在的verilog代码风格里肯定是会包含复位信号的,而且如果有寄存器偶尔忘记给复位,在最开始用modelsim进行前仿真时也可以很快排查出来,但偏偏就有一两个漏网之鱼。

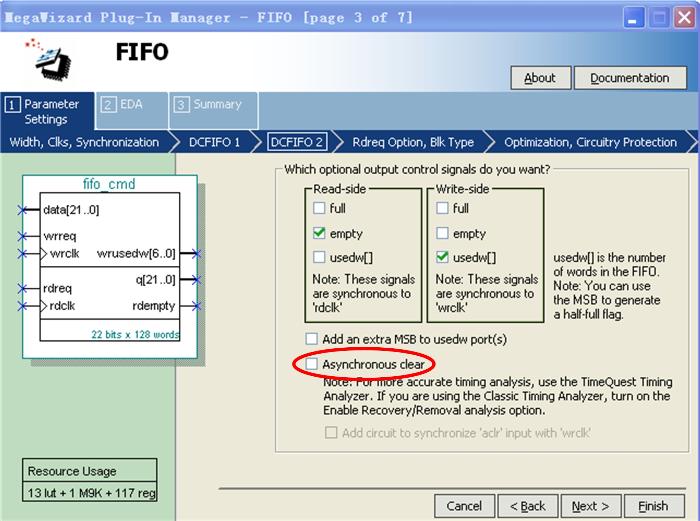

项目里使用了很多个altera自带的fifo模块,发现其中两个fifo模块尽然没有复位信号。。。点开fifo模块发现,缺省情况下fifo模块是没有复位信号的!!由于fifo过多,所以肯定是在创建fifo时,人为的疏漏忘记勾选使能这两个fifo的复位信号了。

正是因为少了复位信号,这两个fifo在开机后处于不确定的状态,让后续的逻辑误取了fifo里的无用数据,导致功能失常。使能这两个fifo的复位信号后,开机不稳定的问题消失了。

虽然问题解决了,属于自己的设计疏漏,但让我疑惑的是,为什么altera给出的权威fifo模块里默认情况下是没有复位清零信号的呢?难道altera不知道一个模块如果没有复位信号上电后会处于不确定的状态吗?而且这类模块复位的问题一般都比较难排查,因为即使没有复位,大多数情况下运行都还是正常的,altera,缺省能给个安全点的fifo,让我们省省心吗?

吐槽完毕。