FPGA与DDR2的硬件连接注意事项

3赞在群里看到有人问起FPGA与DDR2的硬件连接的问题,结合我自己的设计经验,这里以Altera的FPGA为例,简单介绍一下设计方法,抛砖引玉。

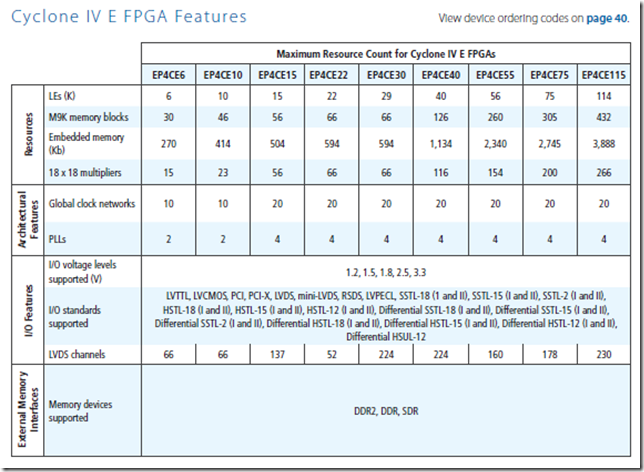

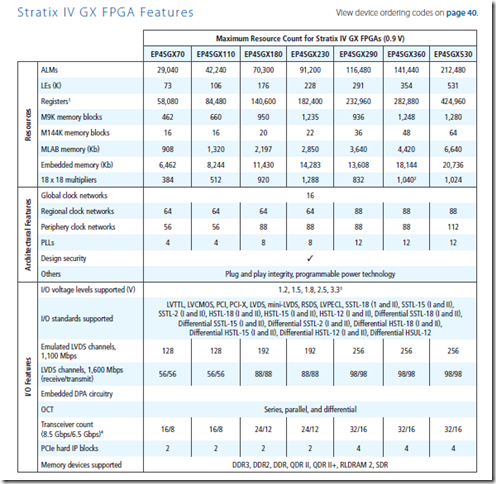

Altera的低端的FPGA一般不支持接DDR3的,而高端的FPGA都是可以支持的,这个可以在他们的选项手册里看到。

这里以我设计的Cyclone 4 原理图为例进行说明,FPGA芯片为EP4CGX110DF27I7,DDR2为MT47H64M16HR,数据线为16bit,用两片组成32bit,用来作为数据的高速缓存。

DDR2的数据线必须连接到FPGA 的引脚名带有DQ的pin;

DDR2的DQS线必须连接到FPGA 的引脚名带有DQS的pin;

DDR2的地址线连接到FPGA 的普通I/O引脚;

DDR2的DM信号连接到FPGA 的引脚名带有DM的pin;

DDR2的时钟、命令等控制信号连接到FPGA 的普通I/O引脚;

一片DDR2连接到一个Bank中,在这里,我用了Bank3和Bank4连接两片DDR2。

EP4CGX110DF27I7共有8个Bank,如下图,

DDR2 四组8位数据依次从低到高:

一二 三 四

3B 5B 4B 2B

那么我们的数据线也按照这样的顺序连接,同样DM、DQS信号也是这样连接,只是位数不一样罢了。尽量让所有DDR2的引脚都在FPGA的同一个或两个Bank区,这样便于对它们分配统一的VCCIO电压,也为了方便后续PCB布线,同时注意该Bank区的VCCIO电压必须指定为1.8V。VREF = 0.9V,VTT = 0.9V。

在Quartus II中,同样也要对这些外接DDR2的引脚进行正确分配,并且还要注意这些电平标准为1.8V。如果硬件设计时不按照这些约束进行相关的引脚分配,在Quartus II编译时,则可能就会报错,而导致DDR2无法正常使用。我为了保险起见,一般是先写一个测试工程,分配和原理图同样的引脚,编译看看,如果大家有更好的方法,麻烦告诉我,感谢。