基于matlab FPGA verilog的FIR滤波器设计

1赞大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

今天和大侠简单聊一聊基于matlab FPGA verilog的FIR滤波器设计,话不多说,上货。

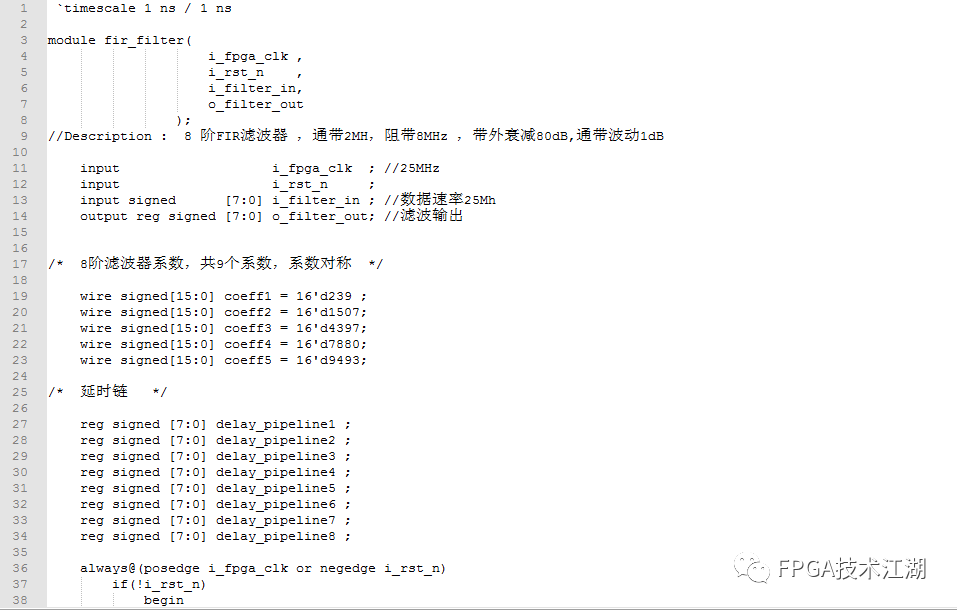

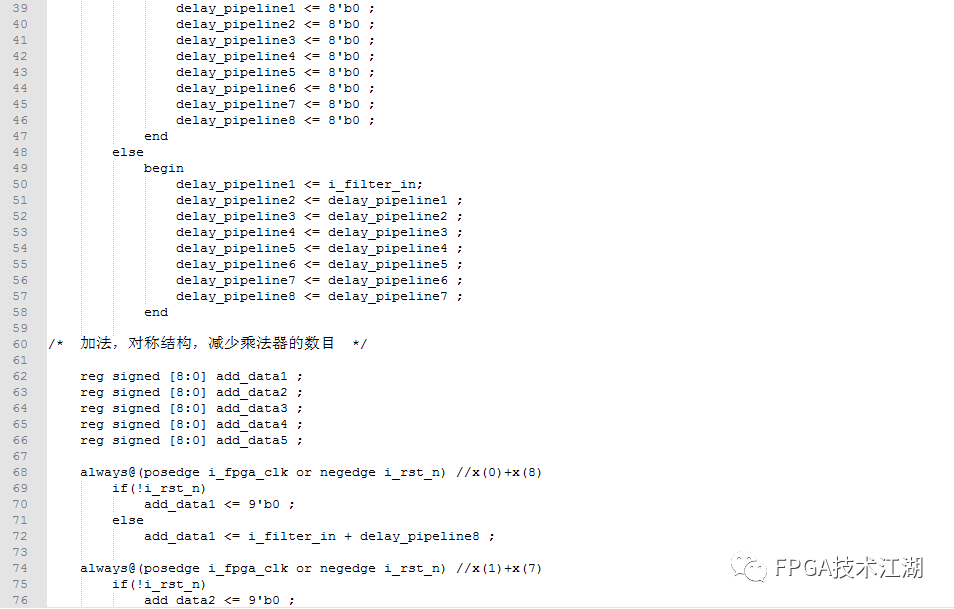

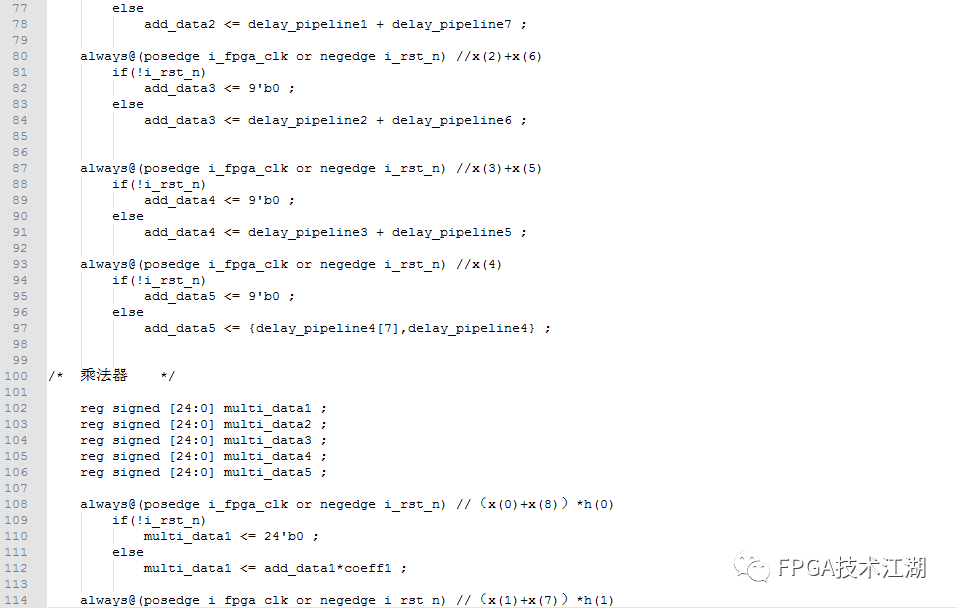

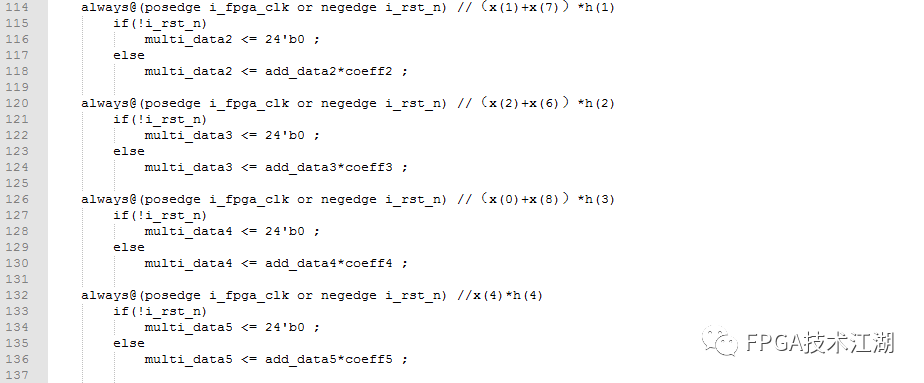

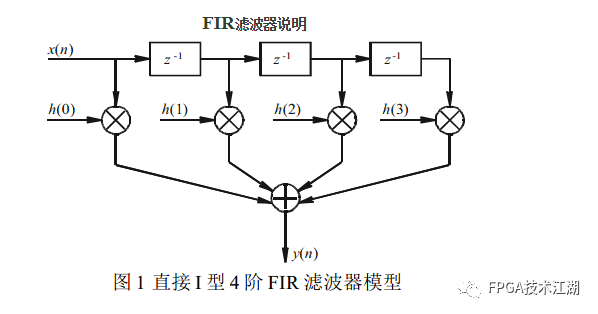

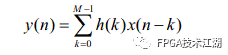

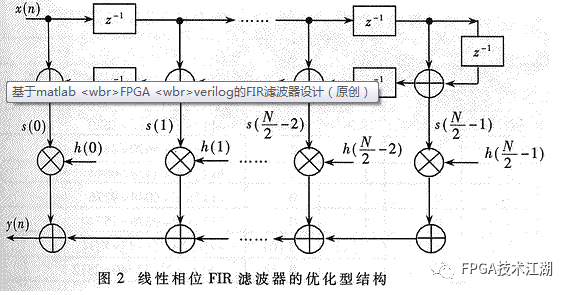

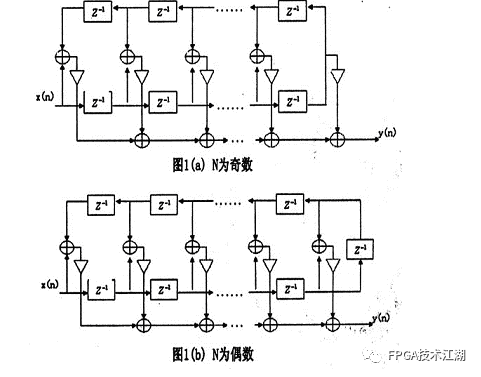

本次设计实现8阶滤波器,9个系数,由于系数的对称性,h(0)=h(8),h1(1)=h(7),h(2)=h(6),h(3)=h(5),h(4)为中间单独一个系数。根据公式:

实现框图:

推导出当系数N为偶数时,例如N=4:y(n)=h(0)*{x(0)+x(n-3)}+h(1)*{x(n-1)+x(n-2)}

当系数N为奇数时,例如N=5:

y(n)=h(0)*{x(0)+x(n-1)}+h(1)*{x(n-1)+x(n-3)}+h(2)*x(n-2)

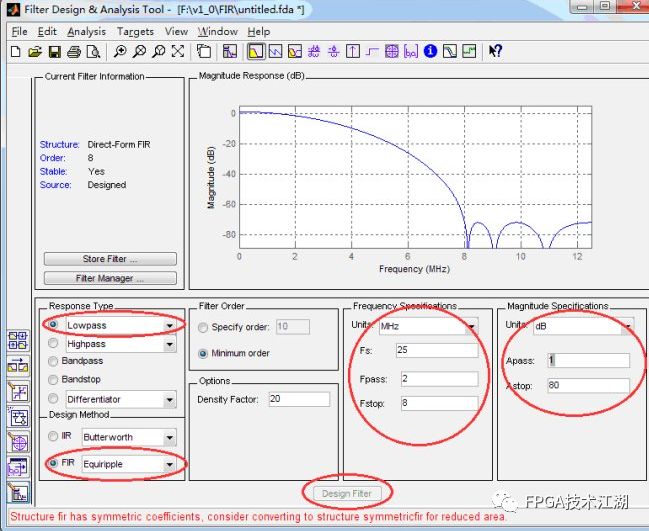

1、用matlab生成和量化滤波器系数

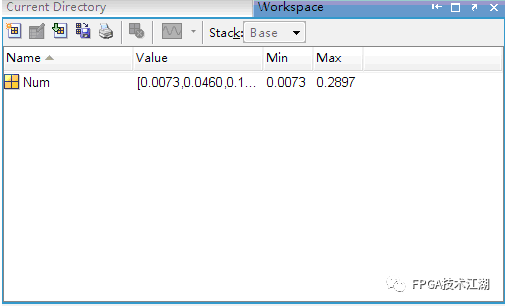

设置参数后,点击“Design Filter”按钮,“file”—“export”,把滤波器系数导出到workspace,如下图:

执行命令:Num=Num’ ,把滤波器系数拷贝到文件COFFICIENT.dat中。

量化系数:在matlab中运行quantization.m

2、说明

用matlab程序sin_1MHz_gen.m生成正弦波波形表,改变变量f0 = 1.5e6可以生成不同频率的波形。把第一个周期的波形数据存入signal_1m.dat文件中,存入的数据个数为Fs/Fo的最小正整数之比的分子,比如Fs=25MHz,Fo=0.3MHz,Fs/Fo=250/3(Fs=25/24MHz),则存入文件signal_1m.dat的波形数据个数为开头的250个数据。相应的signal_gen0.v中的语句if(i0<50)相应的改为if(i0<250)。仿真时signal_1m.dat放在仿真目录下

3、滤波器的multisim仿真

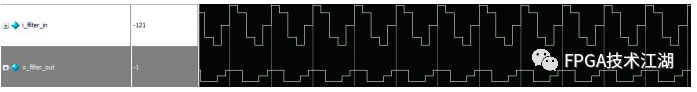

运行matlab,用sin_1MHz_gen.m产生5MHz(f0 =5e6)正弦波信号,Fs/Fo=5,把数据hex_sin_data的前5个数据存入signal_1m.dat文件,相应的signal_gen0.v中的语句if(i0<50)相应的改为if(i0<5)。

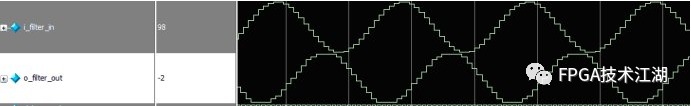

仿真的波形如下图(fir滤波器的输入输出信号):

运行matlab,用sin_1MHz_gen.m产生1MHz(f0 =1e6)正弦波信号,Fs/Fo=25,把数据hex_sin_data的前5个数据存入signal_1m.dat文件,相应的signal_gen0.v中的语句if(i0<5)相应的改为if(i0<25)。

仿真的波形如下图(fir滤波器的输入输出信号):

由此可见FIR对带外信号起到衰减的作用。

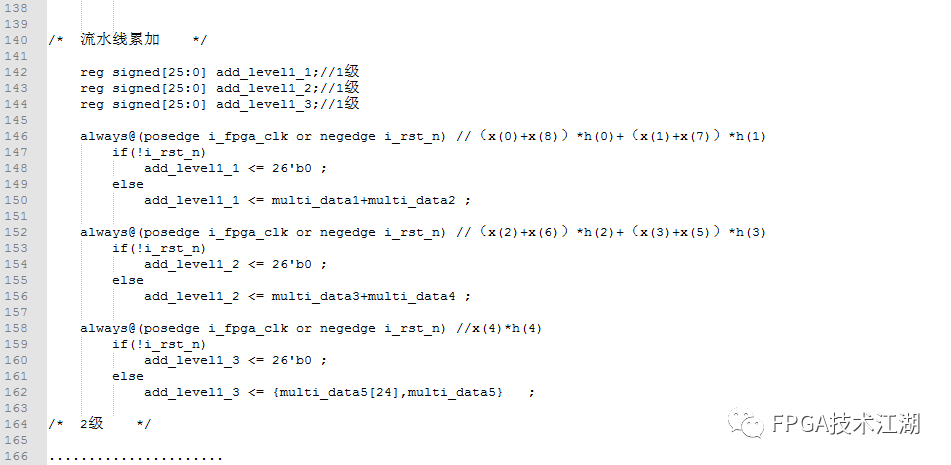

部分代码: