Mathworks 完善代码生成工具家族系列

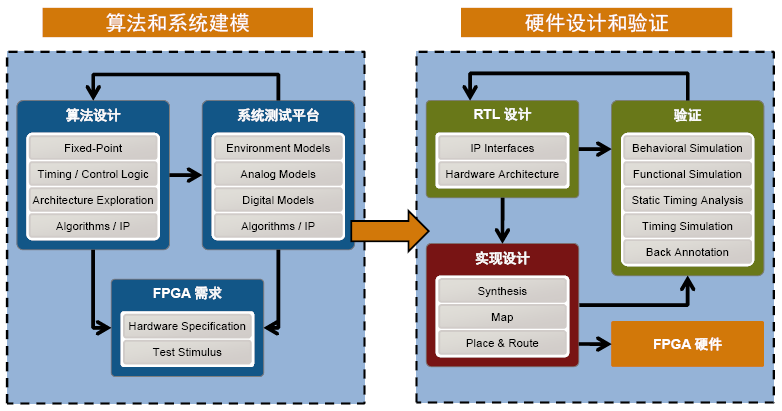

0赞了解系统设计流程的人员都知道,从系统建模到硬件实现的过程是一个设计复杂、需要不断测试与不断调整的迭代过程。作为上层的系统设计工程师,他们侧重于系统本身的性能,关注整个系统的算法设计与系统建模,而非过多得考虑系统的可实现性。但对于硬件工程师来说就不一样了,他们更侧重于整个系统的硬件实现,即在给定指标的情况下将系统以硬件的形式呈现出来,而不去考虑系统性能如何。

正是因为这两类工程师的侧重点不一样,使用的工具不一样,开发流程也是不同的,这就造成了两个环节之间存在巨大的鸿沟。需要浪费大量的时间去迭代,完成设计验证与设计测试。这个过程中还可能需要通过另外一套完全不一样的工具来进行沟通。这种方式使得我们设计或调试一个简单的系统时,可能需要几个星期甚至几个月的时间完成一次迭代。

图1 从系统建模到硬件实现的简化流程

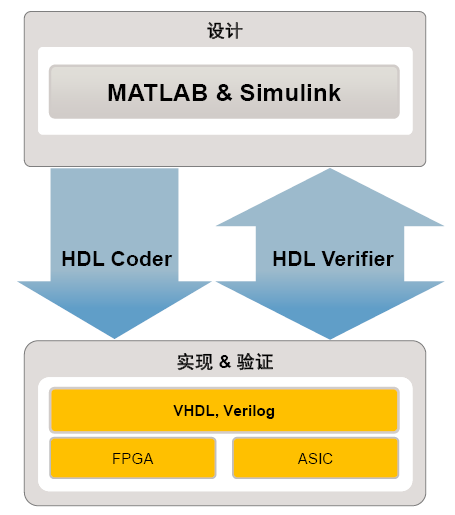

而今年春天Mathworks公司推出的2012a(R2012a) 版 MATLAB 和Simulink 产品系列帮助设计者解决了这一难题。新版本的 MATLAB 和Simulink引进了HDL Coder,可以从MATLAB 或Simulink中 自动生成HDL 代码,用于FPGA 或 ASIC 上的原型设计和实现;此外,还发布了HDL Verifier,用来取代EDA Simulator Link 并增加Altera FPGA 硬件在环支持。有了这两个产品,MathWorks 现在可提供利用MATLAB 和Simulink 进行HDL 代码生成和验证的能力。R2012a 还更新了84 种其它产品,包括Polyspace 嵌入式软件验证产品。

HDL Coder 利用MATLAB 功能和Simulink 模型生成可移植和可综合的VHDL 和Verilog 代码,可用于FPGA 编程或ASIC 原型开发和设计。因此,工程师队伍再也不用手动编写HDL 代码,也不再需要手写HDL测试平台了。就可以立即识别出针对硬件实现的最佳算法。Simulink 模型和所生成HDL 代码之间的可追溯性同时也支持开发遵循DO-254 和其他标准的高完整性应用程序。

这款工具的发布,跨越了系统设计与硬件设计鸿沟。帮助系统工程师在设计的初期考虑更多硬件实现因素,从而使得系统设计更加贴近可实践性。帮助硬件工程师加深对系统全局的理解,真正将精力放在关键之处。它不仅降低了系统设计复杂度、缩短了设计周期,提高了设计效率,还对设计中的一些环节进行了优化,例如浮点到定点的自动转换、算法和HDL之间的可追溯性、HDL资源优化和报告等。

图2 HDL Coder 为FPGA和ASIC设计生成VHDL和Verilog代码

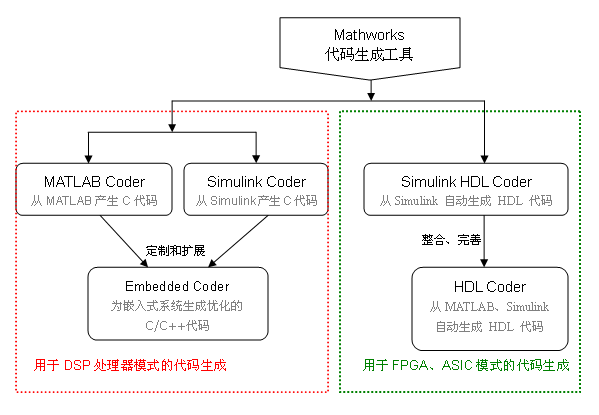

题外话:Mathwork代码生成类工具族谱

HDL Coder与之前的Simulink Coder、MATLAB Coder、Embedded Coder和HDL Coder共同构成了Mathworks代码生成类工具系列。现在我们把集中工具所针对的不同应用领域做一个归纳。

更多信息