Altera DE2试用之时序篇1.

0赞

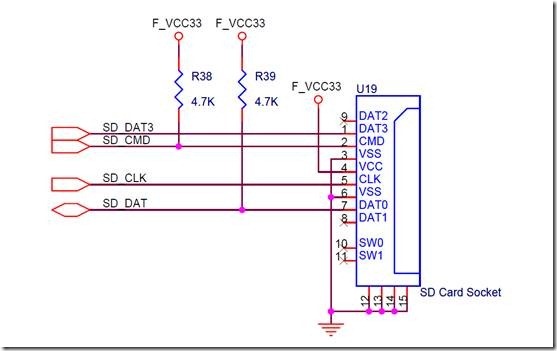

DE2板子有丰富的外设,我们平时设计也离不开外设。本来想写SD卡部分,spi方式控制,读取sd卡的扇区。用硬件逻辑去按照fat16或者fat32的文件系统格式去读很有些困难。DE2提供的例程中,读取sd卡也是采用的nios,还是用c的方式来读的。特权同学的《深入浅出玩转fpga》一书中有个电子相框的实验,将特定大小的bmp图片数据存放在sd卡,通过winhex软件查看到文件的物理地址,然后,将文件大小和文件地址固定到逻辑中去,这样就能实现简单的sd卡图片显示,其实就是把sd卡当作一个spi存储器。

回到DE2上,打通了SD卡、sdram、vga显示器是就可以做这个实验了。开机从sd卡读取图片数据放入sdram中,然后,从sdram中读取缓存的数据到vga显示。为什么要先存到sdram,这是因为sd卡的读取速度有限,在固定的图像刷新速率下,带宽不够。

好了,不说这个了。还是说回时序。

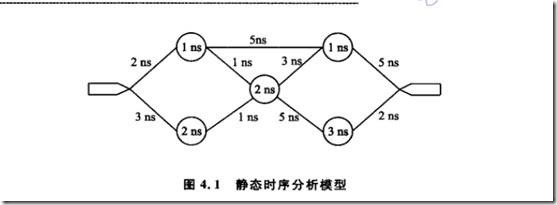

先说为什么会有时序问题。主要是因为信号在传输时会有延时,并且因为传输路径不一样,造成各个信号之间的延时不同。如下图静态时序分析模型:

我们设计的目的,就是要在正确的时间传输正确的数据,所以,要做时序分析。这里有两个基本概念:建立关系值:setup relationship

指的是启动沿 launch edge 到 锁存沿 latch edge 时间长度,比如在上图中,就是从launch到latch的时间6.66ns,因为发送时钟和所存时钟是同一时钟,所以他们之间的值为一个时钟周期,这个是理想的状态。在异步时钟时,有时这个时间会变得很小。这就需要做些约束。

保持关系值 hold relationship

保持关系值指的是下一个launch edge 到 当前latch edge的时间长度。如果发送和锁存采用同一时钟,那么这个时间应为0ns。

(转自Altera FPGA小组,作者:QuietE )