基于ZC706,ZYNQ学习手记(2):用PL端点亮流水灯

2赞--------------------------------------------------分割线--------------------------------------------------------- 开发环境安装好之后,进行大家都喜闻乐见的第一个程序——点灯,本次使用纯逻辑端也就是PL端来控制ZC706开发板上的4个LED灯。

--------------------------------------------------手动分割------------------------------------------------------

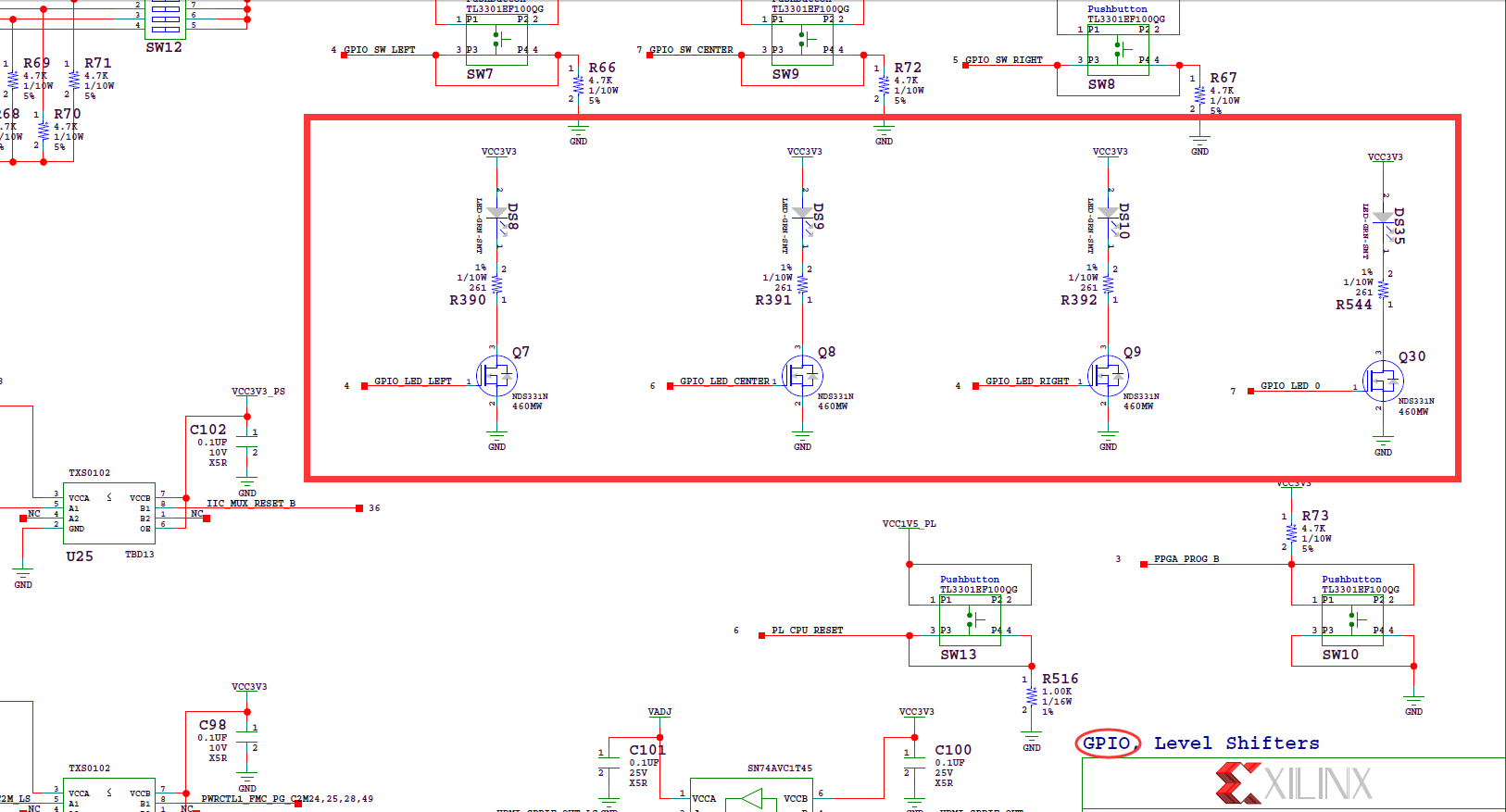

一、查看开发板原理图

![]()

打开之后,找到GPIO页面中四个LED灯位置

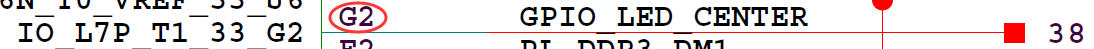

然后找到与LED灯相连的FPGA芯片对应管脚

对应板上从左至右的四个LED灯的管脚分别为Y21、G2、W21、A17。记住这四个管脚,之后在写约束文件也就是XDC文件时需要用到。

同理找到我们需要的外部时钟和复位端口。

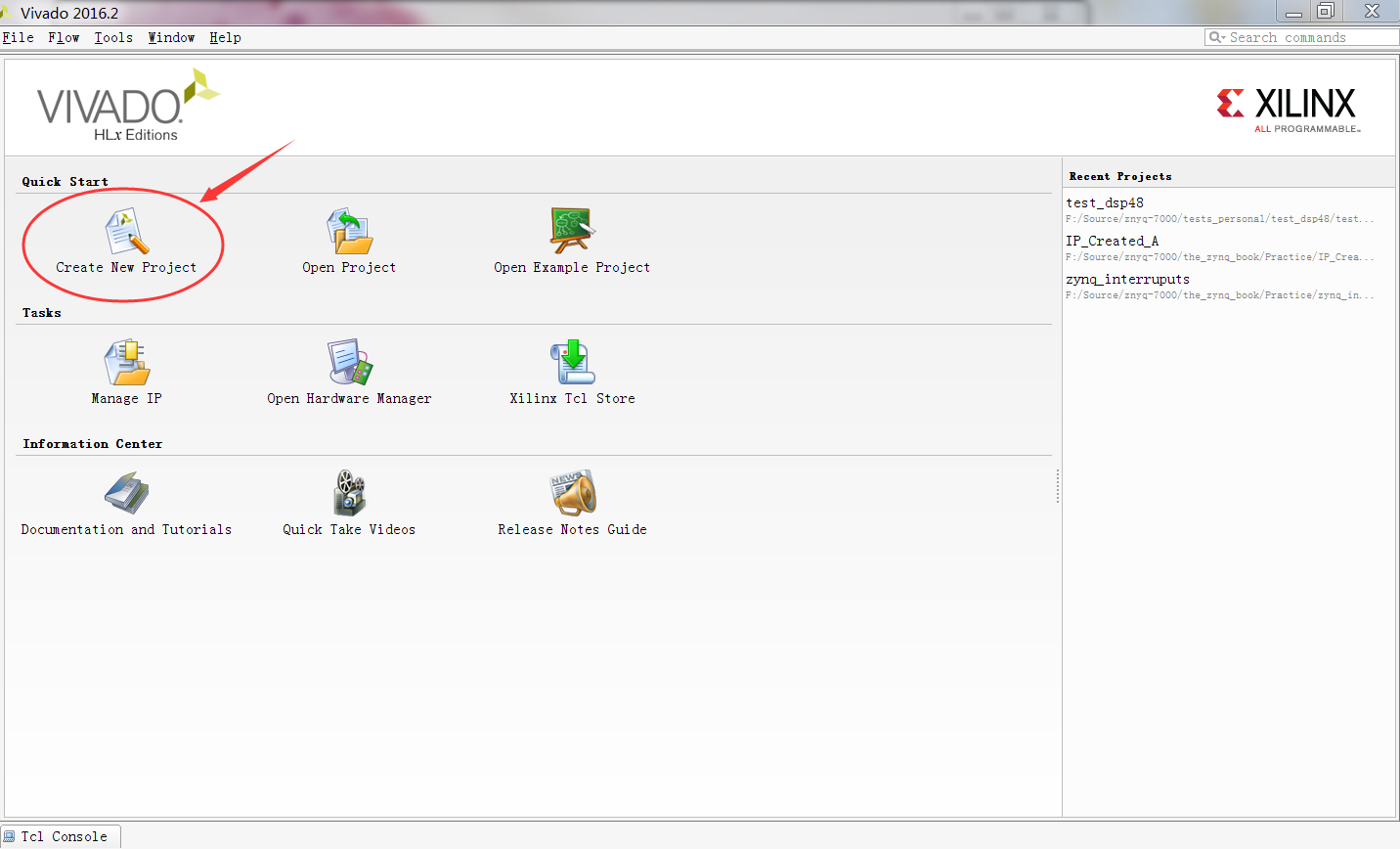

二、新建工程

1.打开vivado![]() 进入初始页面,点击新建工程

进入初始页面,点击新建工程

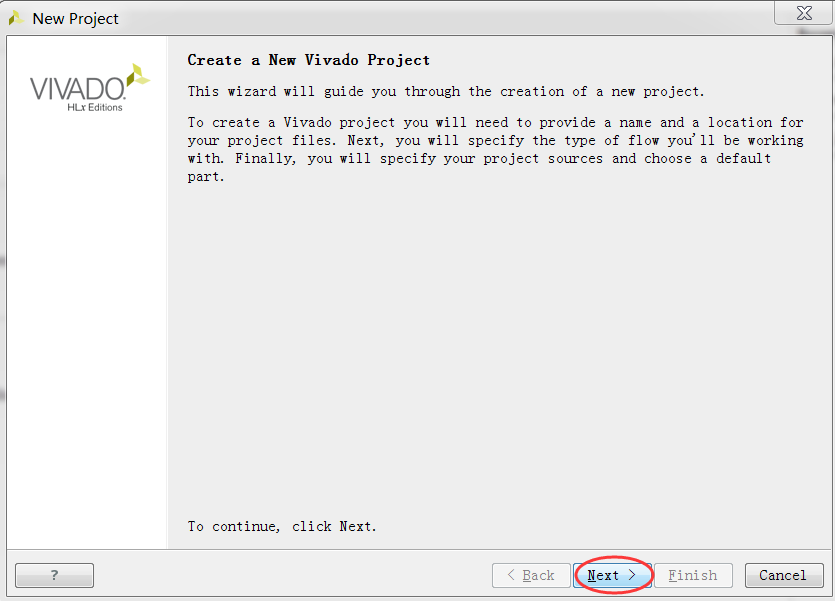

2.弹出向导窗口,直接NEXT。

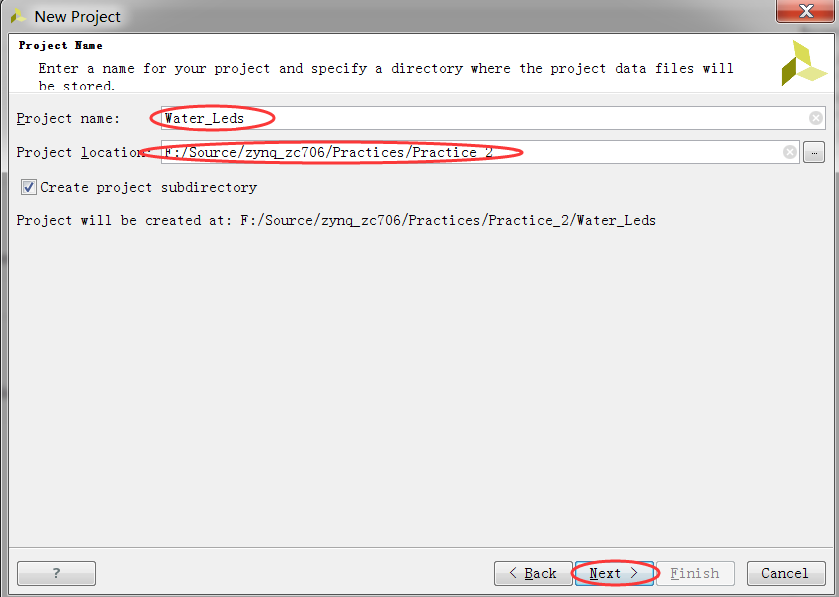

3.设置工程名以及工程路径,楼主在这里设定工程名为Water_Leds,设置好后,点击NEXT

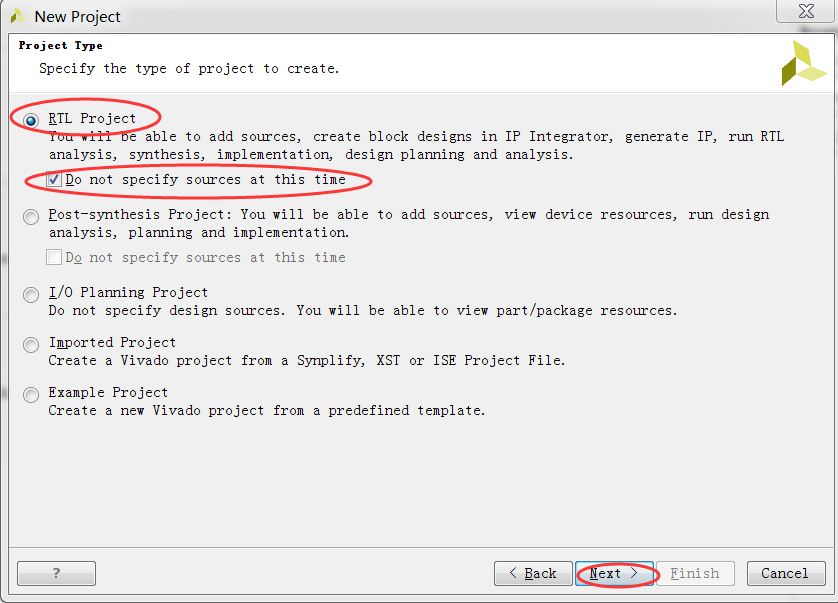

4.选择工程类型,选择RTL工程,这一次先不添加源文件,NEXT

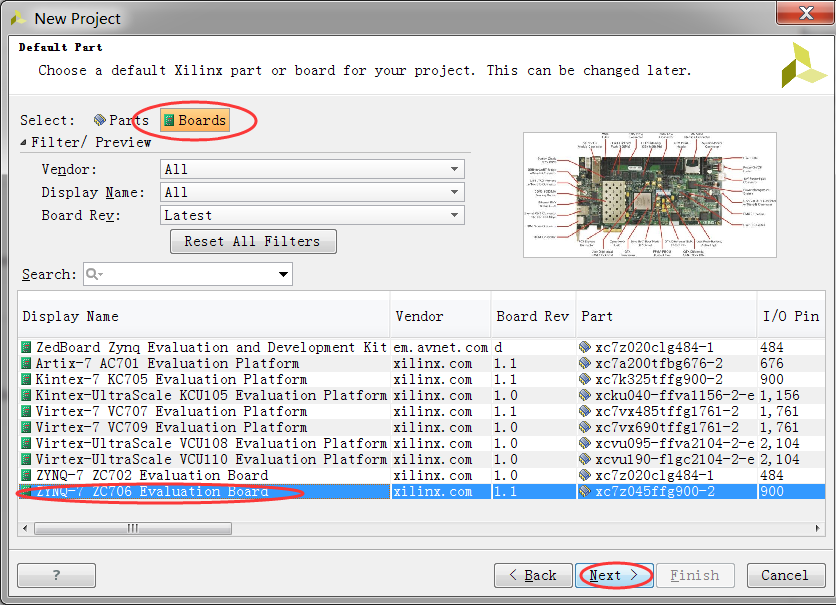

5.选择对应的芯片或者开发板型号,楼主这里选择Boards中ZC706评估板,NEXT

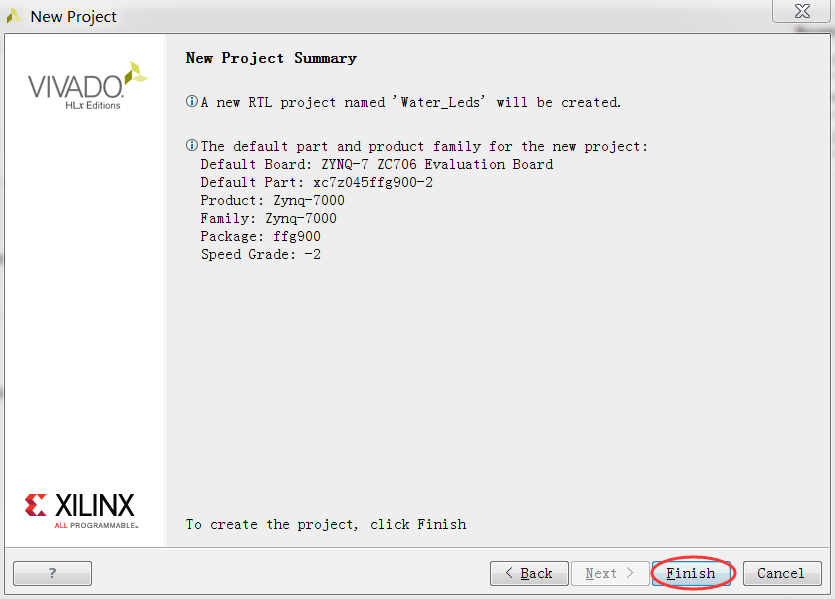

6.最后会弹出一个关于该新建工程的综述窗口,没有问题直接Finish

新建工程的向导就结束了,接下来就是要添加我们的文件到工程中去了。

三、添加文件

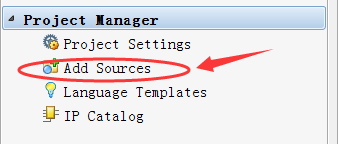

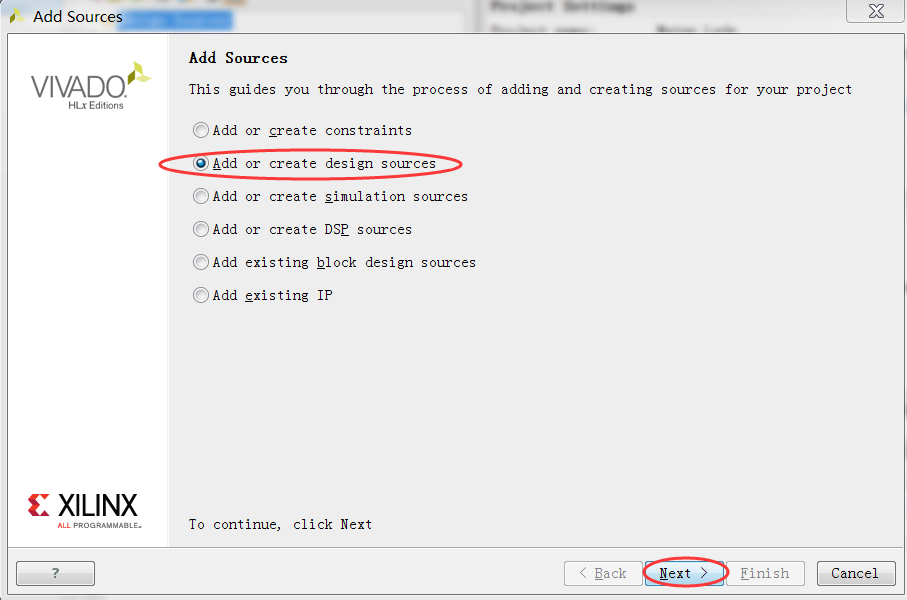

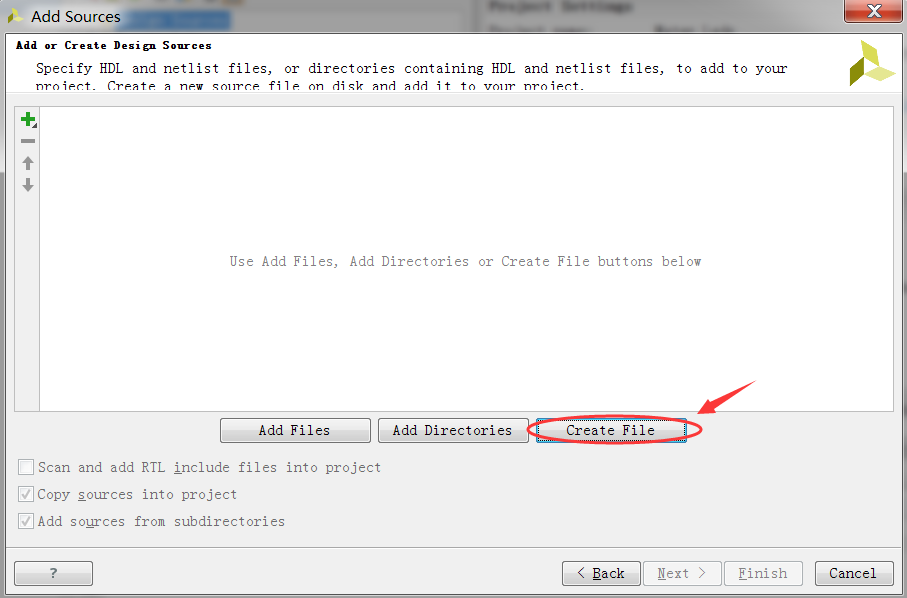

1.添加设计文件也就是我们的.v文件,在工程界面左边Project Manger窗口中点击Add Sources,

或者是快捷键ALT+A,弹出Add Sources窗口,选择Add or create design sources,然后NEXT

如果我们有已经写好的.v文件,可以直接点击Add Files,这里我们要新建一个.v文件,所以选择Create

File,

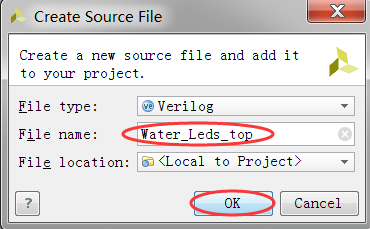

在弹出的小窗口中,输入要创建的文件名(这里楼主填的是Water_Leds_top),然后点击OK

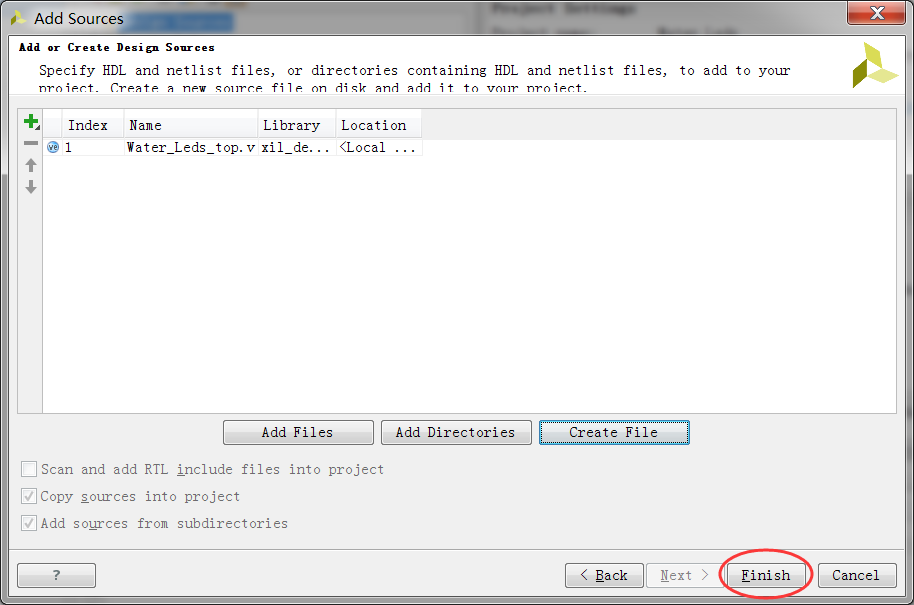

点击Finish

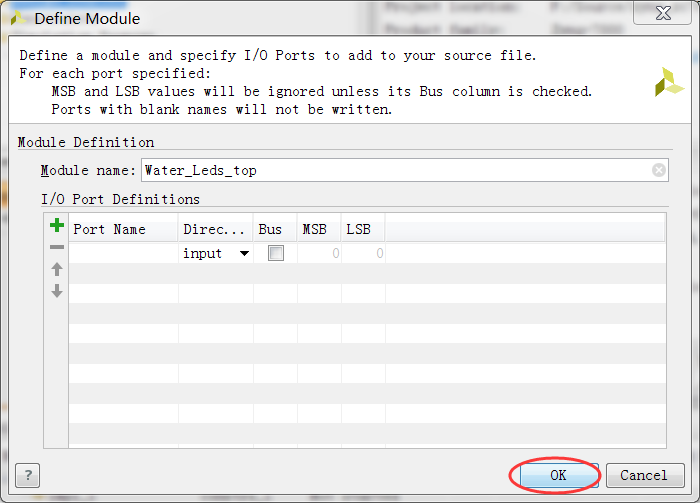

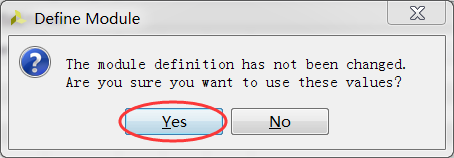

在弹出的窗口中,你可以定义输入输出接口,VIVADO会根据你选择的接口在生成相应的模版,当然,也可以不在这里定义,楼主习惯自己在代码中定义,所以直接点OK,软件会弹出窗口提醒Define Module,直接Yes就好

我们的Water_Leds_top.v文件就已经创建好并添加到工程中了。

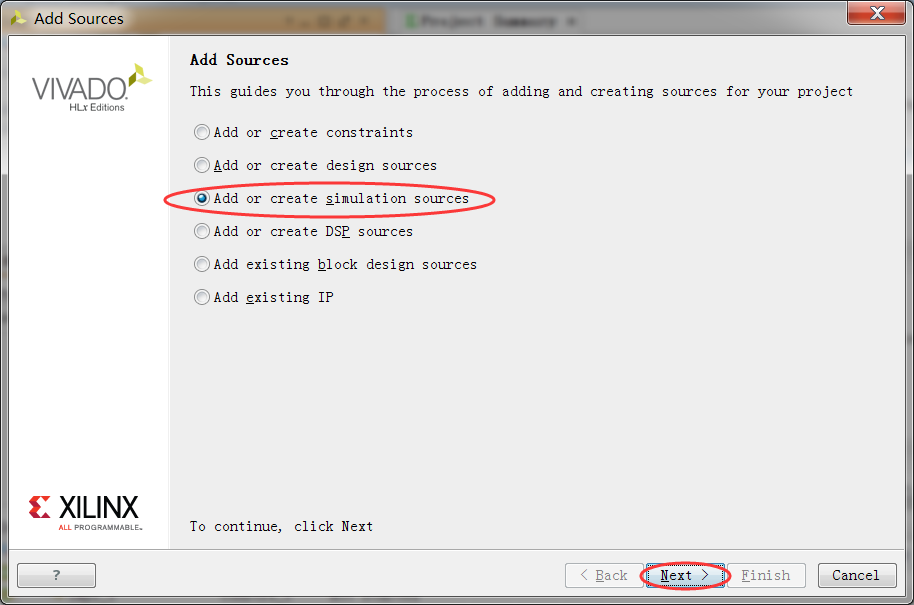

2.添加仿真文件

众所周知,FPGA中仿真是极其关键的一步,接下来说怎么添加test bench到vivado工程中。

与添加设计文件一样,ALT+A打开Add Sources窗口,不同的是,选择Add or create design sources。然后NEXT

后面的步骤跟添加设计文件的过程大同小异,不再赘述。

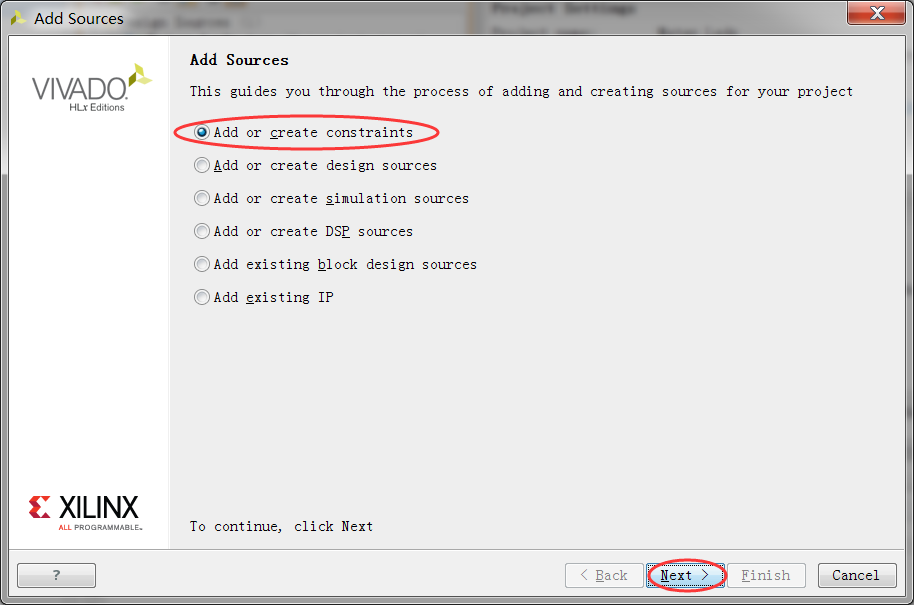

3.添加约束文件

约束文件的添加可以放到功能仿真之后添加,系统综合后打开I/O 配置界面可以用图行化方式配置管脚约束,并自动更新到XDC文件,这次只讲如何创建XDC文件并添加到工程。

与添加设计文件和约束文件相似,ALT+A后选择Add or create constraints。

之后步骤也与之前一样。

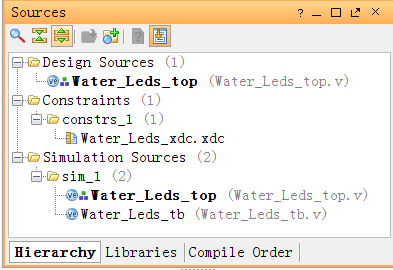

当文件都添加到工程后,我们可以在Sources 窗口中看到刚刚添加的文件,双击后就可以编辑

四、编辑文件

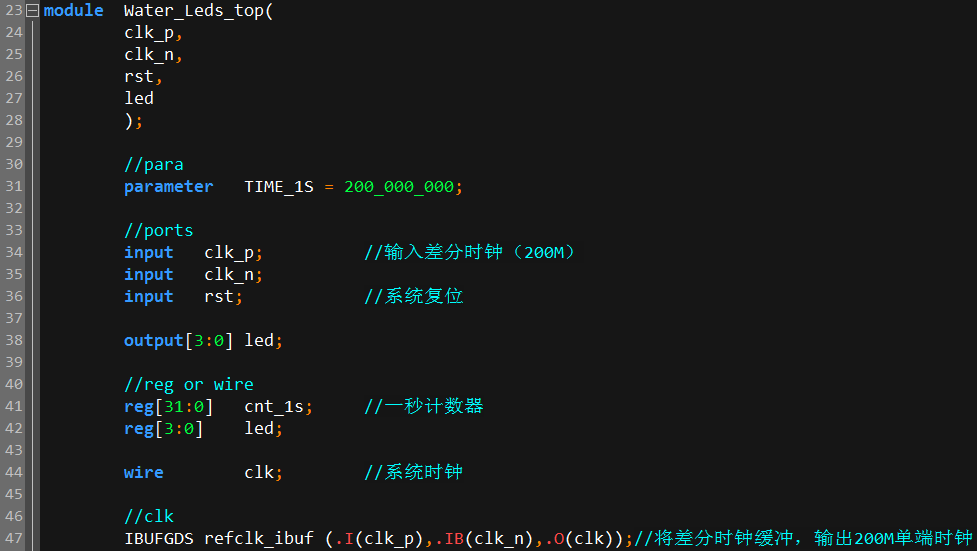

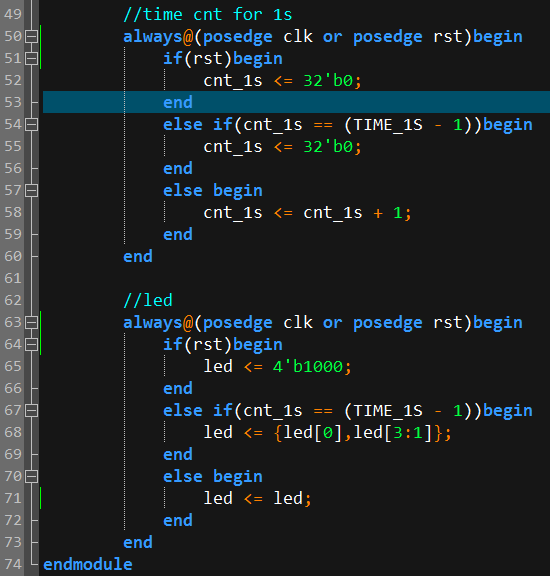

1.编辑设计文件(逻辑设计代码)

双击打开Water_Leds_top.v后,添加设计代码到文件中。

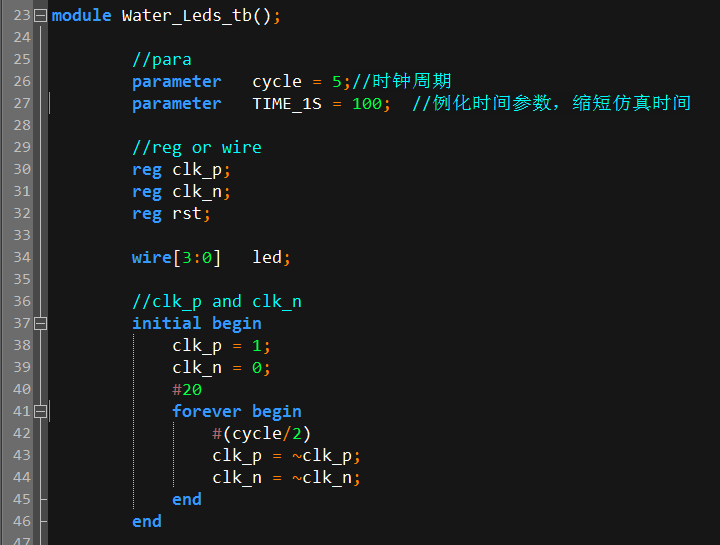

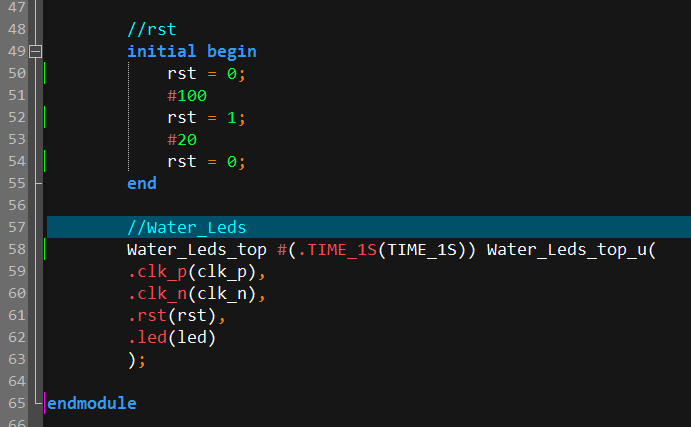

2.编写test bench

同样的,双击打开Water_Leds_tb.v后,添加相关代码到仿真文件

这里由于仿真一秒的时间太长了,所以在test bench 中将时间参数例化为100个时钟周期。

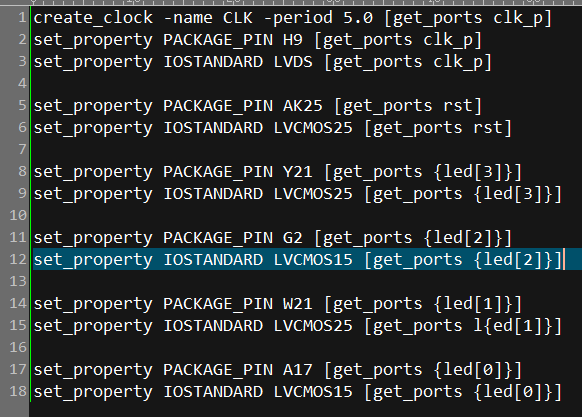

3.编写xdc文件

vivado中约束文件是xdc文件,与ISE的ucf文件还是有些差别的,不过xilinx官方提供了相关的xdc文件

打开

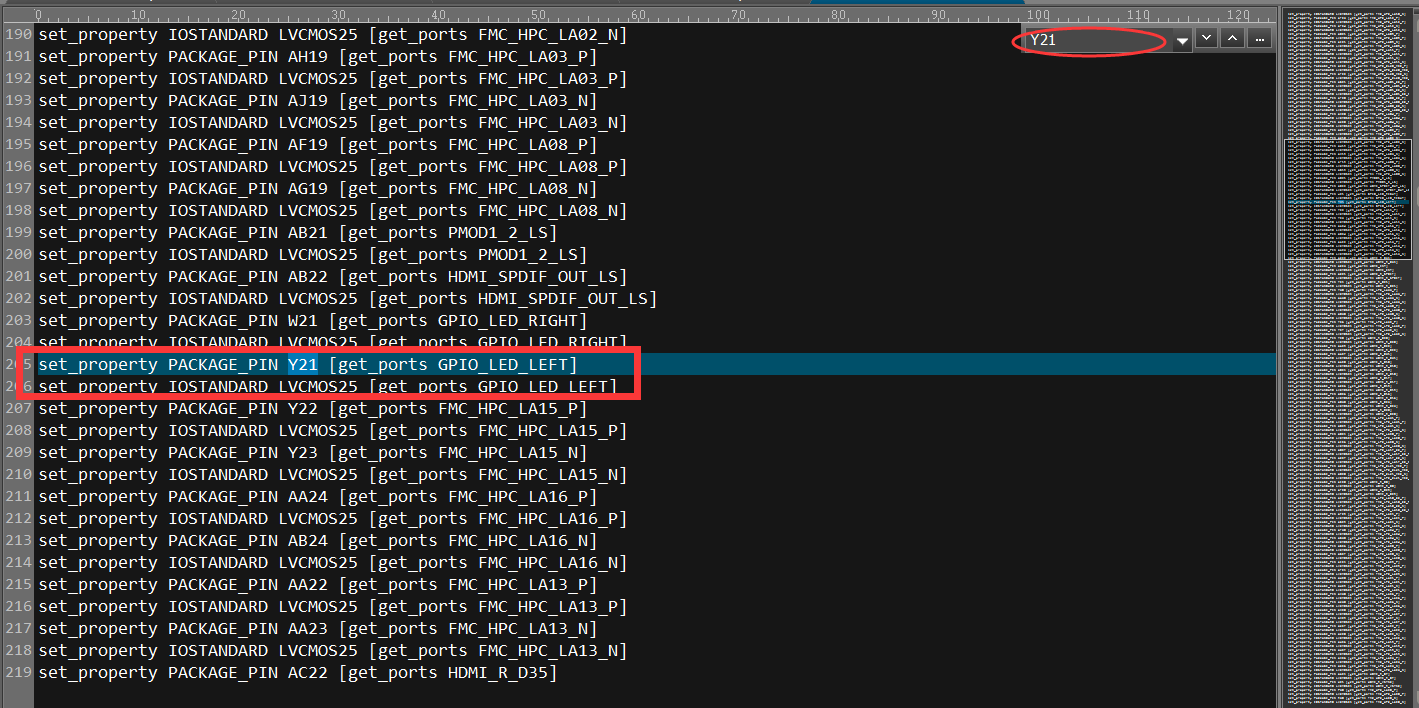

其中是已经写好的XDC文件,里面记载了相关端口的电气参数,我们只需要将自己需要的语句copy到我们的xdc文件中就好了,根据前面led连接到芯片端口号搜索,这里以Y21为例

将其端口设置为与我们设计中led[4]口相连。。其余端口也类似。。。

这就是我们需要的Water_Leds_xdc.xdc文件了。

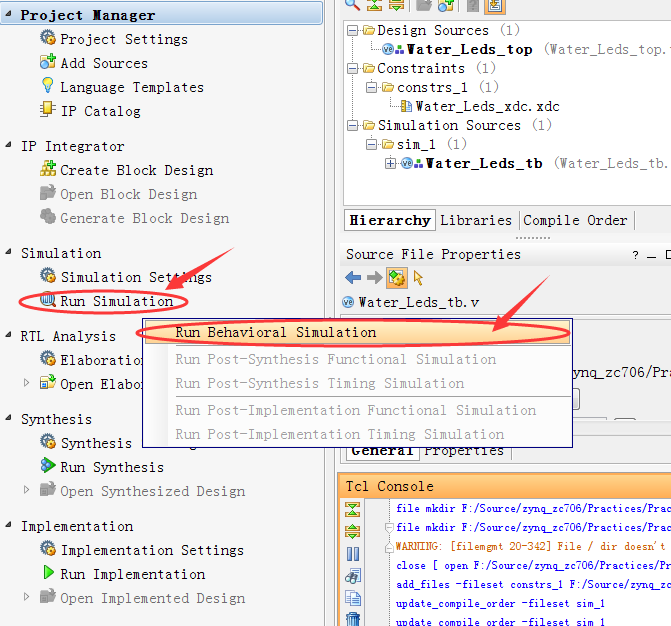

五、仿真

设计文件和仿真文件添加好后,就可以进行行为仿真来验证逻辑是否正确了,本次用VIVADO自带的Vivado simulator作为仿真工具。

如图所示,打开行为仿真。

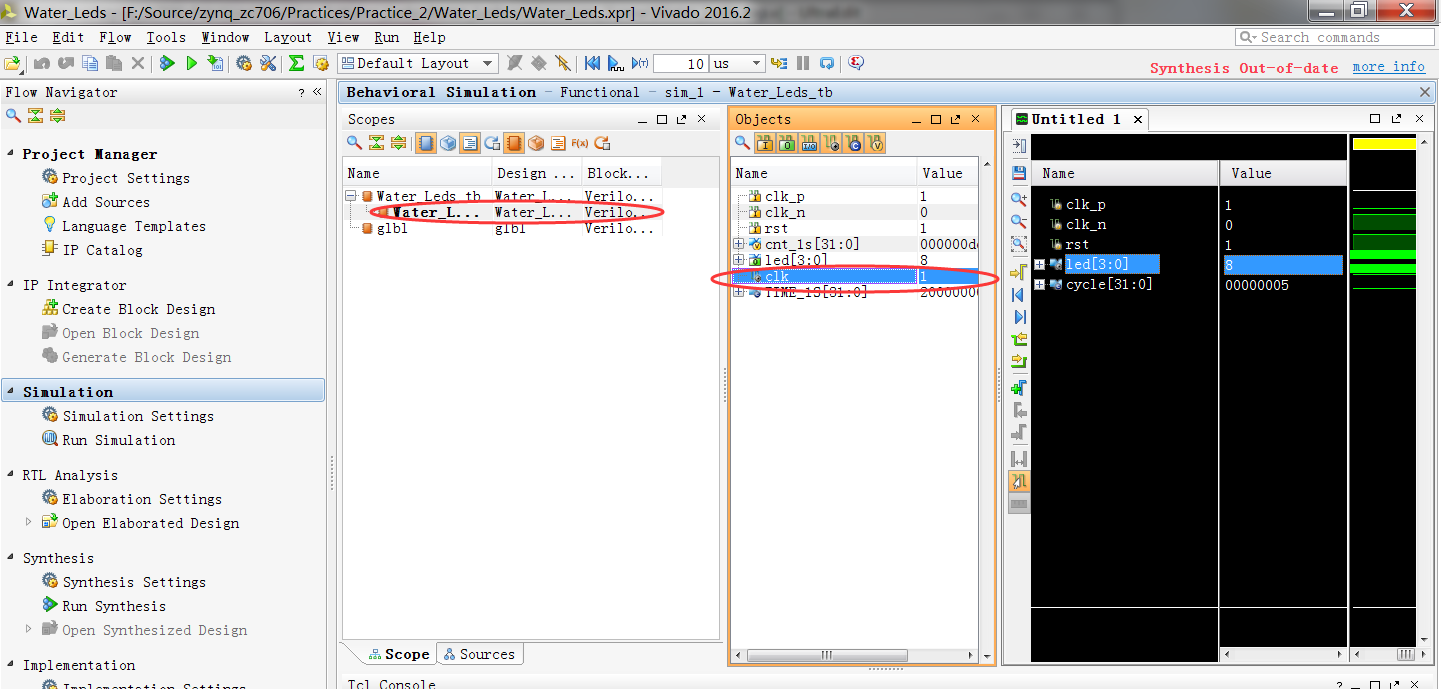

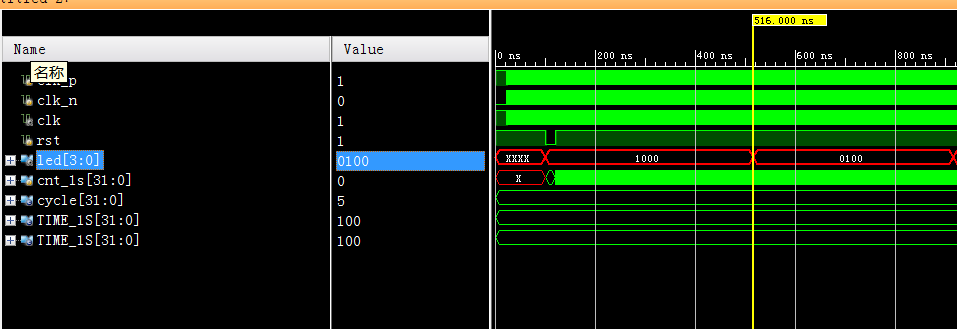

稍等片刻,出现仿真界面,添加感兴趣的信号到波形窗口(可以直接拖拽)

复位后开始仿真,三个蓝色的按钮,第一个是复位,第二个是马上开始仿真(不限时间),第三个是仿真到制定时间,这次我们只仿真10us。

完成仿真后,放大波形窗口,观察波形。可以通过边上的按钮来放大或者缩小时间刻度,也可以直接用CTRL+滚轮来控制。

当然,这只是行为仿真,只用来查看是否有逻辑错误。在工程综合和实现后,还可以分别进行加入线上延时以及约束后的仿真,更贴进片上实现的效果。也可以通过插入ILA核或者VIO核来做片上逻辑仿真,这个我们以后再提。

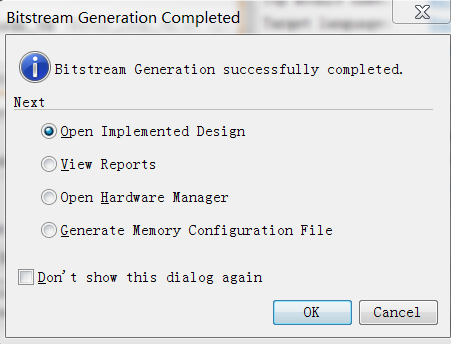

六、综合,实现,生成bit文件

在vivado界面的工具栏

这三个键分别对应综合、实验、生成bit流文件。

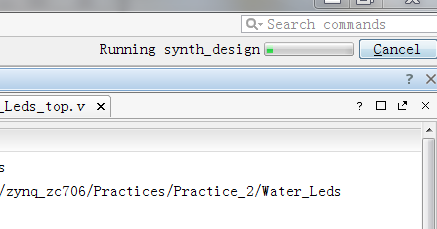

一次点一遍或者直接点击生成bit文件,然后就是漫长的等待。。右上角有它的进度,如果中途报错了,查看错误提示并检查你的代码

这里说一下,如果逻辑仿真没问题而实现不能通过,一般都是约束文件那边出问题。

成功后会弹出小窗口,关掉然后就可以下载文件到板子上了

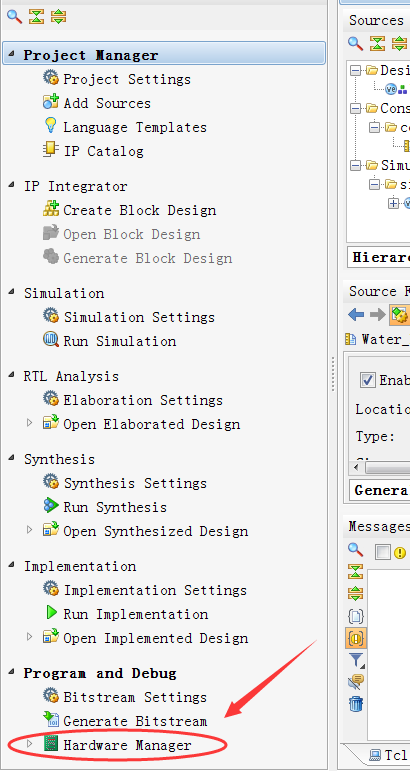

七、上板测试

bit文件生成好了,接下来就是上板测试了,找到Open Hardware Manager

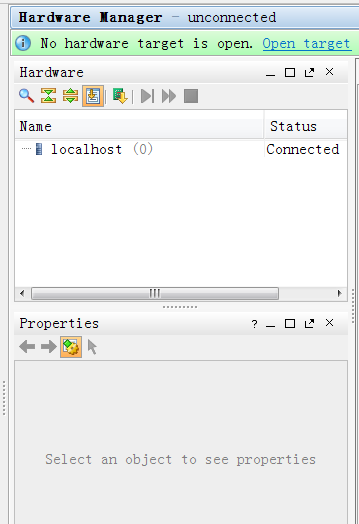

打开后点Open Target 然后点Auto Connect,

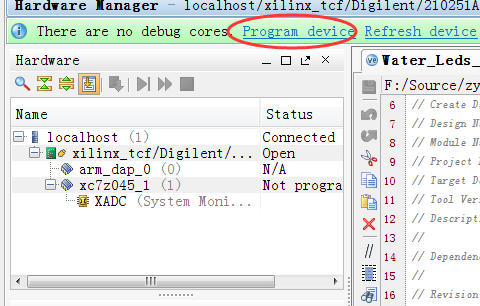

没找到。。。什么鬼?哦,原来是开发板没上电,将开发板的usb jtag口连到PC上,上电,再次点链接,这次有了

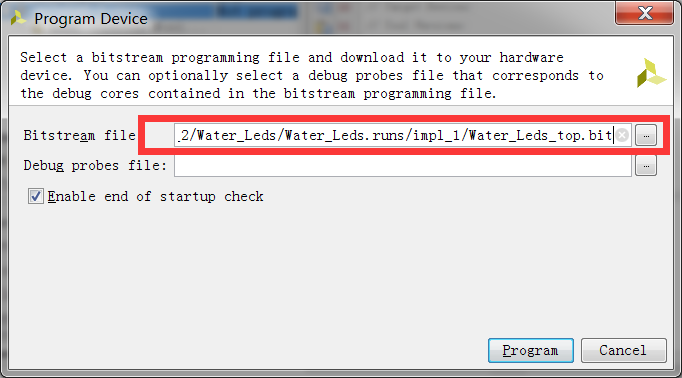

直接点Program device,然后点下拉出来的xc7z045_1,弹出下面的窗口

注意检查bit文件的路径,千万别弄错了。

这次我们没有添加ILA或者VIO核,所以没有degug 文件,直接点Program就好了。

下载中。。。。

下载完后,就能看到板子上,电源边上的那四只LED灯在从左往右的闪啦。

---------------------------------------------再割----------------------------------------------------------------

这么简单一个工程,为了写这个博客居然用来两个小时。。。好累,希望能坚持写下去。。。

相关代码上传到附件了。