【原创】Vivado高效设计案例-----XJTAG的简化边界测试

0赞AET又有新活动,鼓个掌,太给力了。

Vivado作为赛灵思的新的拳头产品,可提供全新构建的SoC 增强型、以 IP 和系统为中心的下一代开发环境,以解决系统级集成和实现的生产力瓶颈. Vivado Design suite 在 总体生产力、使用简易性和系统级集成能力方面领先一代。

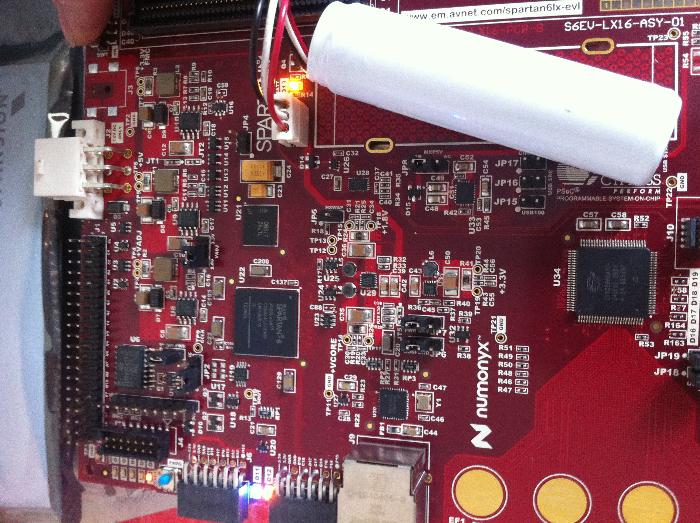

忍不住把我的神器拿出来给大家分享一下,伴我度过了很多美好的日子,现在都非常棒的FPGA产品。

再设计中非常有意思的一个案例分享给大家:

XJTAG 公司的工程师与赛灵思公司密切使用,基于 开发板开发了几种立即可用的测试脚本,支持XJTAG 边界扫描测试解决方案用户从 System Monitor 访问数据。 XJTAG 可以直接将片芯温度、供电电压和片外模拟量数值显示在工作站上,从而可以方便地验证System Monitor 和XJTAG 采集的数值在规定的容限内。

下面是常见的一段简单的测试脚本代码,用来检查FPGA 的工作参数。用户可利用XJTAG 的高层脚本语言XJEase 来生成所需要的脚本。 在以下中的Test 函数中,首先配置System Monitor。 然后读取相应的输入并检查之。

//----------------------------

Test()(INT result)

//----------------------------

INT temp;

result := 0;

Config_SysMon()();

Read_Internal_Temp()(result);

Read_VAUX()(result);

Read_VINT()(result);

Read_RefP()(result);

Read_RefN()(result);

IF (result != 0) THEN

result := RESULT_FAIL;

ELSE

result := RESULT_PASS;

END;

END;

下面的代码显示出如何利用XJEase 脚本语言设置和测试某些System Monitor输入以下的代码检查器件的温度。 如果温度超出容限,测试过程中会显示错误。 这一例子给出了如何利用XJTAG 网站上提供的简单功能来使用FPGA 的Monitor 功能。XJTAG 还支持定制测试。例如,记录System Monitor 数据用于故障检测或跟踪。通过创建脚本可以让XJTAG 检查峰值、响应阈值或在SystemMonitor 获取的数据上使用平均算法。

下面是用于测试FPGA 温度的代码段

//----------------------------------------------------------------------

-----------

Read_Internal_Temp()(INT result)

//-------------------------------------------------------------------------

--------

INT temp;

Read_Temp()(temp);

IF ((temp < (Die_Temp - Temp_Margin)) || (temp > (Die_Temp + Temp_Margin))) THEN

PRINT(“Die temperature =“ ,temp,”C. ** OUTSIDE LIMITS **\n”);

result := result + 1;

ELSIF (DEBUG) THEN

PRINT(“Die temperature =“ ,temp,”C\n”);

END;

END;//----------------------------------------------------------------------

-----------

Read_Temp()(INT temp)

//-------------------------------------------------------------------------

--------

Read_Channel(0)(temp);

temp := ((temp * 20159) / 40960) - 273;

END;

做为XJTAG 环境的一部分提供的XJEase 方便了脚本的创建。 XJEase 支持以更高层抽象语言操作原始边界扫描数据。 无论器件是否在边界扫描链上,都可以创建针对特定器件的测试脚本。 这些脚本可以存储起来,并且可供未来项目重利用。

每当网表数据显示板上有变化,XJTAG 都会自动生成新的测试序列,从而节约了手工重写测试程序所需要的时间。 与此相比,较早的边界扫描测试设备生成的测试序列通常是与板的设计有关的,每次设计修改都需要

进行更新,即耗时又费力。

随着这一面向器件的扫描方法在工程师群体的测试开发过程中越来越普及,许多XJTAG 用户已经开发将经过验证的预编写脚本发布到XJTAG 网站上。 与XJTAG 签有技术支持合同的客户可以免费从www.xjtag.com

网站下载这些脚本并将其集成到自己的测试程序中。 同时,如果网站上没有你所需要的完全相同器件的脚本,那么只需要简单地下载一个类似的脚本,然后再针对待测器件进行定制修改就可以了。

这个功能我希望能在Vivado的板子上跑一跑,去年掌握了这个方法以后我在很多的FPGA上测试过,希望能有机会在Vivado上在跑一跑,相信一定能有非常好的表现,谁让人家是赛灵思呢?