《FPGA那些事儿--TimeQuest静态时序分析》之读后感(上篇)

0赞关注《FPGA那些事儿--TimeQuest静态时序分析》这本笔记也快一年了,虽然之前并不叫这个名字,呵呵。

之前就是觉得写的好,但是其中还是有很多不明所以的地方。

上周完成了USB通讯之后,对时序有了一些新的认识,以前一直把Verilog当作一个完美的工具在用,并没有考虑物理上的时序延时,

趁着USB的余热又把TimeQuest从新认识一遍。

以下内容是我个人在反复阅读《FPGA那些事儿--TimeQuest静态时序分析》之后的一点理解,所有的截图都是截自原文。

写这篇文章的目的有如下几点:

1、向akuei2致敬,表明我们大家都很关注他的文章,望再接再厉多出精品,造福我们这些“小白”,嘿嘿。

2、发表一些自己的看法,自我总结,大家一起学习讨论。

3、说出自己曾经的困惑,帮助和我有同样困惑的人。

言归正传:

首先我要定义一下“理想建立关系值”和“理想保持关系值”

“理想建立关系值”定义——没有任何布线延时的情况下,原寄存器的启动沿与目的寄存器的锁存沿之间的值!

“理想保持关系值”定义——没有任何布线延时的情况下,源寄存器下一个启动沿和目的锁存沿之间的距离。

这两个定义是我理解akuei2思维的关键!

之前一直对askei2的什么建立关系值什么保持关系值有疑问,今天似乎有突破性的理解!

就从建立关系值说起吧!

首先,必须明白一点:作者并没有说两个寄存器都是FPGA内部的!,也就是说这两个寄存器可能一个是FPGA的,一个是外部芯片的!确定这一点是理解下面的关键!!

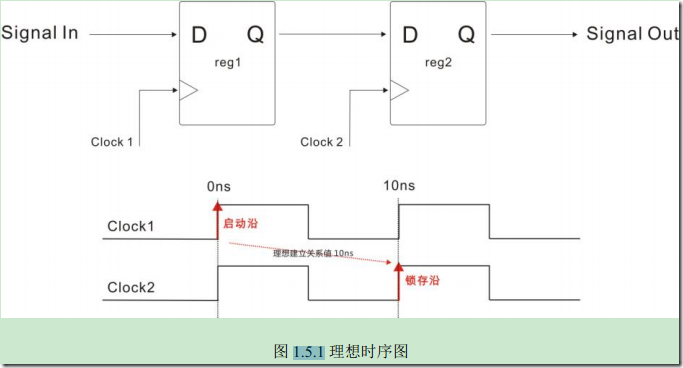

假设一、如果说这个是内对内模型,也就是说这两个寄存器都是FPGA内部的!那么Clock1和Clock2他们的起点是一样的,都是由FPGA的时钟延时而来,作者也强调了

是相同的时钟源,因为是理想的所以没有任何延时,导致Clock1和Clock2的启动沿在同一个时间点,那么理想建立关系值为一个时钟,也就是上图的10ns。这被作者称为

理想建立关系值下的理想时序!紧接着作者理想建立关系值下的物理时序!

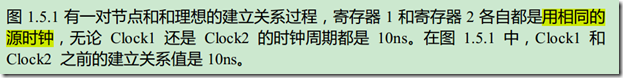

这里我当时就有点纳闷,因为建立关系值的定义是:原寄存器的启动沿与目的寄存器的锁存沿之间的值!Clock1和Clock2既然有了不同的延时,那么建立关系值就不可能为10,但是注意这是“建立关系值”

而不是“理想建立关系值”,请不要向我一样,把两者的关系搞混淆了,呵呵。

(PS:这句话是运用公式的关键)所以我们要用到的是“理想建立关系值”。

作者明确给出了“建立关系值”但是却没有明确给出“理想建立关系值”的定义!这是导致我之前不理解的主要原因。

好吧,不扯了,呵呵!是我太笨的缘故。

回顾,一开始的定义:

“理想建立关系值”定义——没有任何布线延时的情况下,原寄存器的启动沿与目的寄存器的锁存沿之间的值!

“理想保持关系值”定义——没有任何布线延时的情况下,源寄存器下一个启动沿和目的锁存沿之间的距离。

所以不管Clock1和Clock2的路径延时是多少(只要延时的起点是样的),“理想建立关系值”不会变!

还有一点 作者其实有提示,观看图1.5.2,Clock1和Clock2延时的起始点是一样的!也就是说明reg1和reg2用的是用一个时钟源!

也可以这么理解只要reg1和reg2用的是用一个时钟源那么,Clock1和Clock2延时的起始点是一样的,那么“理想建立关系值”就是10(一个时钟)。

接下来,就可以理解askei2所谓的时钟偏移了!!!

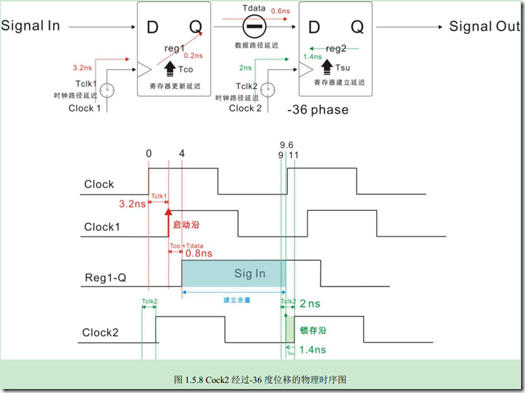

这幅图的“理想建立关系值”是9,既然是理想的为什么Clock1和Clock2延时的起始点不一样??!!

并不是有延时,“理想建立关系值”的取得是没有任何延时的存在的,那是为什么Clock1和Clock2延时的起始点不一样??!

这个原因很简单,Clock1和Clock2来自不同的时钟源!那么这个偏移就可以理解了!!接下来就是见证奇迹的时刻,

对比图1.5.8和图1.5.2,明显发现Clock1和Clock2延时的起点是不同的,也正好也1.5.7吻合!!这种情况就是,两个寄存器的时钟源不同,且考虑各种延时的情况。

再来用作者的公式,来求建立余量和保持余量,心里就有底气多了。

先从最简单的开始,假设两个寄存器用的是同一时钟源,也就是延时起点是一样的情况,我来求它的建立余量:

观察上图Clock1和Clock2延时的起始点相同,可知“理想建立关系值”为一个时钟周期,假设一个周期是10ns,那么 理 想建立关系值 = 10;

建立余量 = (锁存沿 + Tclk2 - Tsu) + (启动沿 + Tclk1 + Tco + Tdata)

= (理想建立关系值 + Tclk2 - Tsu)+ (0 + Tclk1 + Tco + Tdata)

= (10 + Tclk2 - Tsu)+ (Tclk1 + Tco + Tdata)

观察以上公式,锁存沿时刻就是理想建立关系值,启动沿不用说就是时间的起点0.

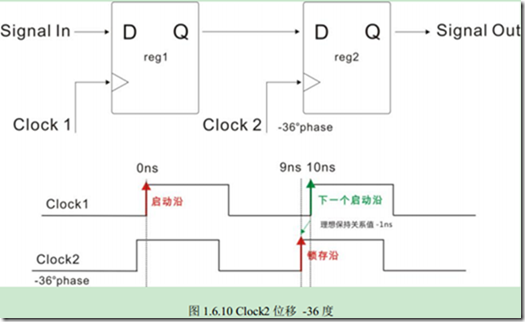

但如果说,reg1和reg2用的本不是一个时钟源,在没有任何延时的情况,两时钟就存在偏移量,如下图:

Clock2,也就是目的寄存器的时钟比源寄存器的时钟延时了1ns,这种情况下公式不变,唯一便的是

锁存沿时间,抑或说是理想建立关系值不同了,此时理想建立关系值就是11ns

建立余量 = (锁存沿 + Tclk2 - Tsu) + (启动沿 + Tclk1 + Tco + Tdata)

= (理想建立关系值 + Tclk2 - Tsu)+ (0 + Tclk1 + Tco + Tdata)

= (11 + Tclk2 - Tsu)+ (Tclk1 + Tco + Tdata)

紧接着,看保持余量如何求:

同样的,观察上图Clock1和Clock2延时的起始点相同,可知理想保持关系值为0(理想建立关系值就是10)

那么:(注意这里保持余量是屁股求法)

保持余量 = (启动沿 + Tclk1 + Tco + Tdata)-(锁存沿 + Tclk2 + Th)

= (0 + Tclk1 + Tco + Tdata) -(理想保持关系值 + Tclk2 + Th)

= (0 + Tclk1 + Tco + Tdata) -(0 + Tclk2 + Th)

= (Tclk1 + Tco + Tdata) -(Tclk2 + Th)

观察以上公式,启动沿不用说永远是0重点观察锁存沿,锁存沿时间,对于求保持余量而言,等价于理想保持关系值。就像求建立余量时,

锁存沿时刻等价于理想建立关系值。如果说,reg1和reg2用的本不是一个时钟源,在没有任何延时的情况,两时钟就存在偏移量,如下图:

由理想保持关系值的定义:“没有任何延时的情况下,原寄存器的启动沿与目的寄存器的锁存沿之间的值!”

可知理想保持关系值为-1ns,同样公式不变,应用即可:

保持余量 = (启动沿 + Tclk1 + Tco + Tdata)-(锁存沿 + Tclk2 + Th)

= (启动沿 + Tclk1 + Tco + Tdata)-(理想保持关系值 + Tclk2 + Th)

= (Tclk1 + Tco + Tdata) -(-1 + Tclk2 + Th)

总结:

1、如果reg1和reg2用的同一个时钟源,那么它们的“理想建立关系值”就是一个时钟周期,“理想保持关系值”就是0

2、如果reg1和reg2用的不是同一个时钟源,那么一开始就存在偏移是正常的,这时可根据定义求得“理想建立关系值”和“理想建立关系值”

3、求建立余量时,锁存沿时刻就是等价于“理想建立关系值”

4、求保持余量时,锁存沿时刻就是等价于“理想保持关系值”

未完待续~~~