【技术分享】Verilog打造TFT接口1

0赞说明下,我的TFT所用的控制芯片是SSD1289,用纯 Verilog驱动,不用nios。

首先,必须介绍下SSD1289,我看网上很多资料都是介绍ILI9325的,介绍SSD1289

的比较少,我找了好久,找到了一个介绍SSD1289的帖子写不错~~

http://forum.eepw.com.cn/thread/209537/4

这里在它的基础上,我也好好总结下:

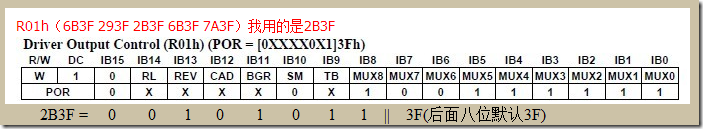

先来看看几个总要的寄存器:

总结:这个寄存器主要是设置,扫屏时的扫屏顺序。

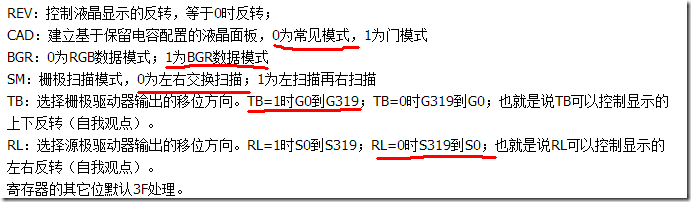

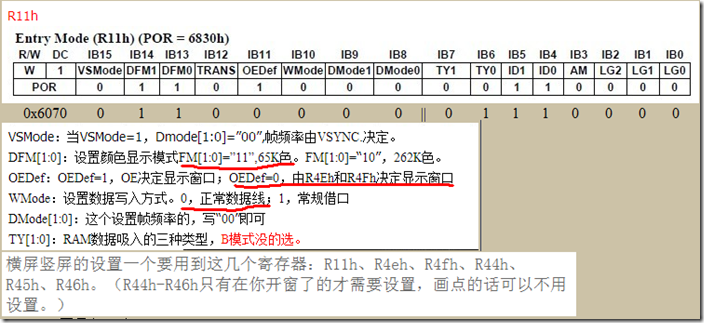

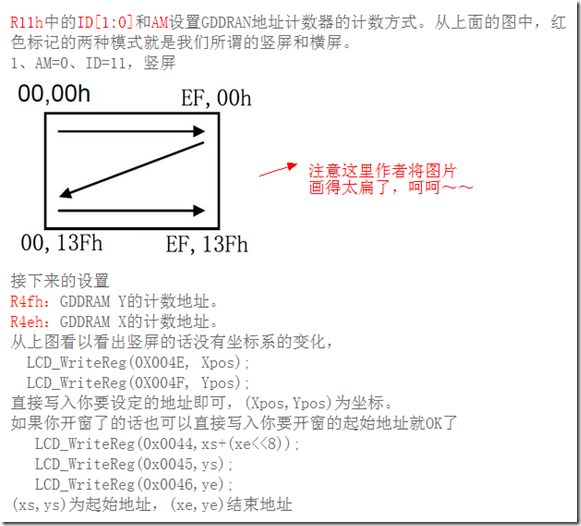

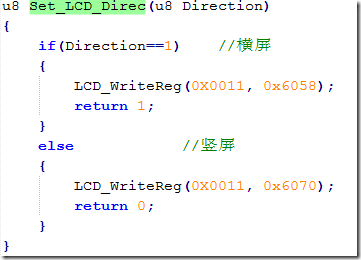

0x6070设置是竖屏,如下:

总结:这个寄存器,主要是设置横屏,竖屏。

也就是说:当寄存器R01 = 2B3F; 且R11 = 6070时,那么你的屏将

是一个竖屏,且扫描方式是从上到下,从左到右,我想这样的设置是最

正常的,呵呵~~

接着来:

R00h :晶振使能,0x0001打开晶振,0x0000关闭晶振。

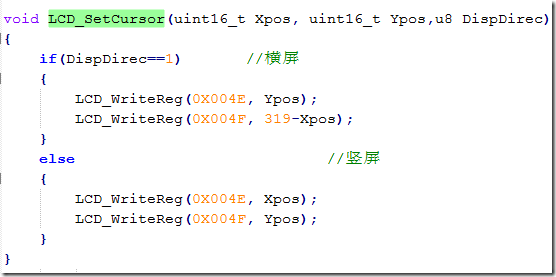

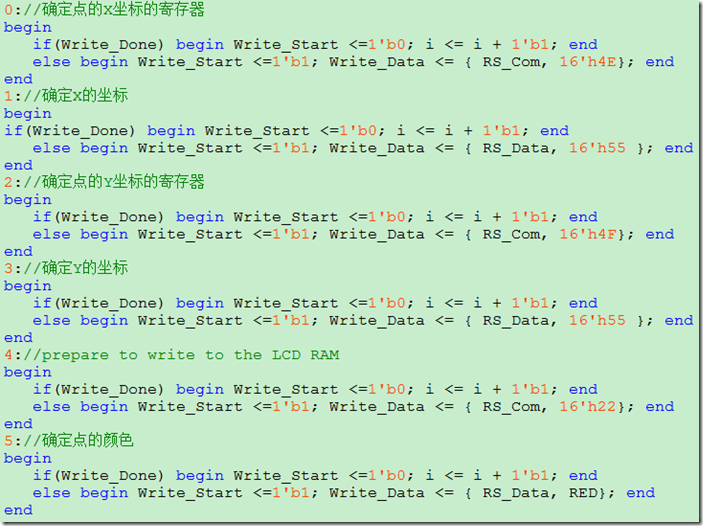

R4eh:设置GDDRAM X的计数地址。

R4fh:设置GDDRAM Y的计数地址。

这两个寄存器用于设定画点的位置

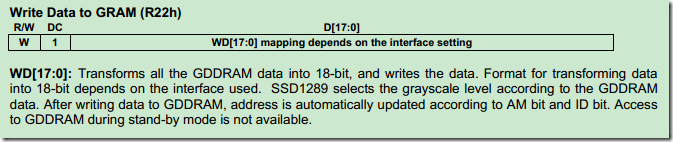

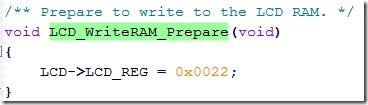

R22h:用于确定这个点的颜色

假设初始化完成之后,我想画一个点:

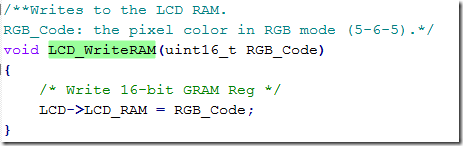

用C来写就是这样:(我们是竖屏,只看竖屏部分)

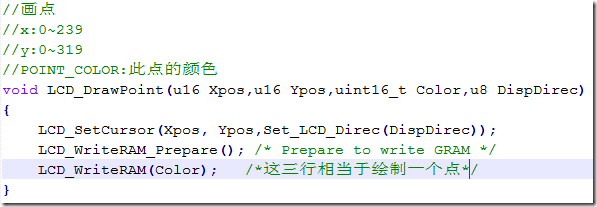

用Verilog来写就是这样:

上面这段话的意思就是,在坐标(55,55)的这个位置打一个红色的点~~以上

这段程序不必深究,领会下就行,主要是为了解释R4eh,R4fh,R22h,这几个寄存器的

用法~~

当然,这都是后话,TFT还没初始化呢?

先介绍下要用到哪些引脚:

我们要用的引脚是:

#TFT复位信号: RST(硬复位TFT)

#TFT片选: CS(片选信号)

#命令数据选择 : RS (低命令,高数据)

#TFT写信号 : WR(向TFT写入数据)

#TFT读信号: RD(从TFT读取数据)

#TFT数据总线: DB[15:0](16位双向数据线)

现在就是如和通过芯片的这几个引脚,让FPGA把数据发给TFT,

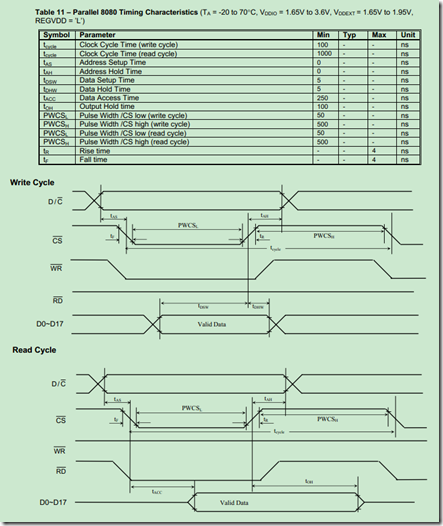

那么请看8080并行接口时序~~

8080并行接口的发明者是INTEL,该总线也被广泛应用于各类液晶显示器。

模块的8080并口读/写的过程为:先根据要写入/读取的数据的类型,设置RS 为高(数据)/低(命令),然后拉低片选,选中SSD1289,接着我们根据是读数据,还是要写数据置RD/WR为低,然后:

在RD的上升沿, 使数据锁存到数据线(DB[15:0])上;

在WR的上升沿,使数据写入到数据线(DB[15:0])上;

根据上面的时序要求,最后贴上我的写数据模块:

1: module TFT_Write2: (3: input CLK,4: input RSTn,5: input [16:0]iData,//{1'TFT_RS,16'TFT_Data}6: input Start_Sig,7: output [18:0]oData,//{1'TFT_CS,1'TFT_RS,1'TFT_WR,16'TFT_Data}8: output reg Done9: );10:11: reg CS; //驱动TFT片选12: reg WR; //驱动TFT写信号13: reg [15:0]Data; //驱动TFT数据总线14: reg [3:0]i;15: always @(posedge CLK or negedge RSTn)16: if(!RSTn)17: begin18: CS <= 1'b1;19: WR <= 1'b0;20: Done <= 1'b0;21: i <= 4'd0;22: end23: else if(Start_Sig)24: case(i)25: 0:26: begin27: CS <= 1'b0;28: WR <= 1'b0;29: i <= i + 1'b1;30: end31: 1:32: begin33: Data <= iData[15:0];34: i <= i + 1'b1;35: end36: 2://延时20ns,拉底CS 60ns,CS的读周期,最小是100ns37: begin38: i <= i + 1'b1;39: end40: 3,4,5://保证CS拉高60ns,这样读的CS周期就大于100ns了~41: begin42: CS <= 1'b1;43: WR <= 1'b1; //WR的上升沿数据锁存44: i <= i + 1'b1;45: end46: 6:47: begin48: Done <= 1'b1;49: i <= i + 1'b1;50: end51: 7:52: begin53: Done <= 1'b0;54: i <= 4'd0;55: end56: endcase57:58: assign oData = {CS,iData[16],WR,Data};59:60: endmodule接下来就运用这个模块,去控制TFT吧~~

未完待续~~