【红色飓风Nano二代测评】DCM PLL 时钟简单应用--led流水灯

0赞前些天玩了一下DCM PLL IP的配置,实现了时钟分频。这里简要讲述一下xilinx DCM IP的配置方法和简单的应用。步骤如下:

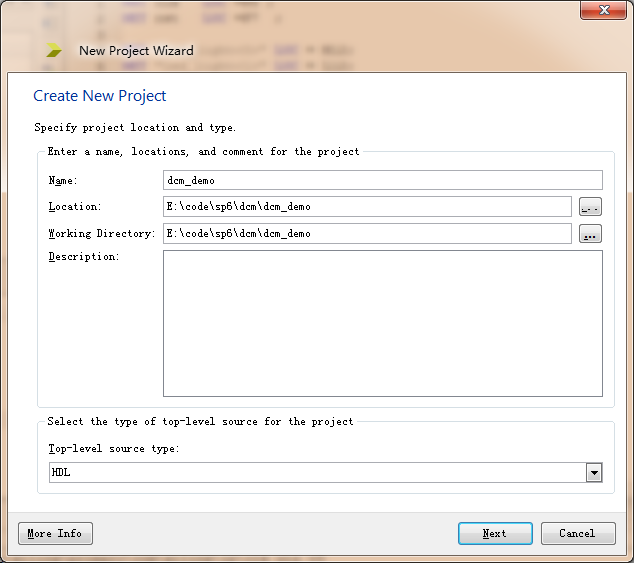

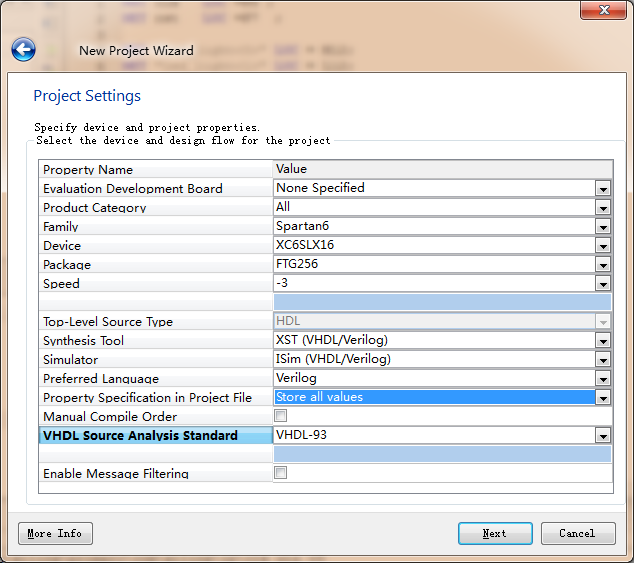

1:打开ISE,新建一个新的project

2:next,选择器件类型和封装。

3:next,finish。

4:给project添加文件,首先添加IP核文件。右键点击工程,新建文件,new source.出现如下添加文件类型选项

5:点击 IP (core generator & architecture wizard),并且在file name 里面写上需要写的 IP核文件的名称。点击 next;出现如下图

6:选择需要的IP核

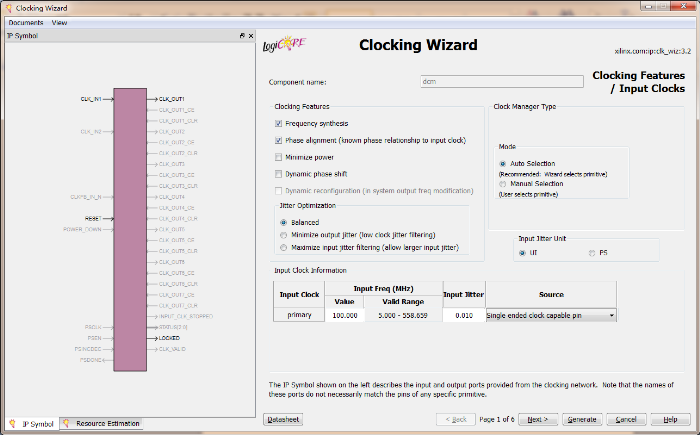

7:点击next,finish。出现如下图(此时开始配置IP核):

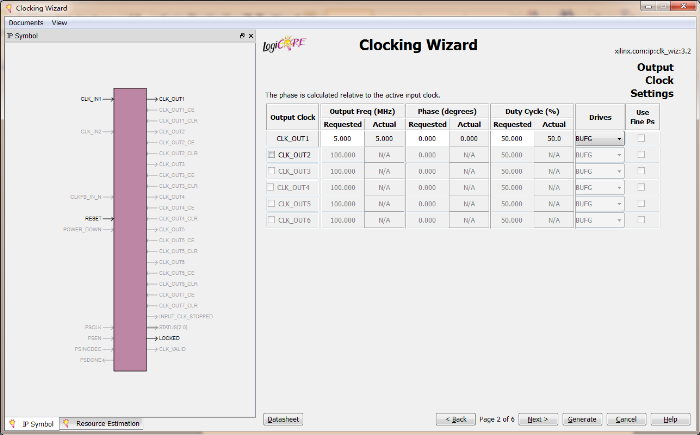

8:由于我们的时钟输入的是50MHz 所以,在Inpur Freq 要修改位 50。点击next,output Freq 设置为5,phase 设置为0,Duty cycle 设置为 50%。只需要一个输出值,当然如果需要的话,可以设置多个输出值。

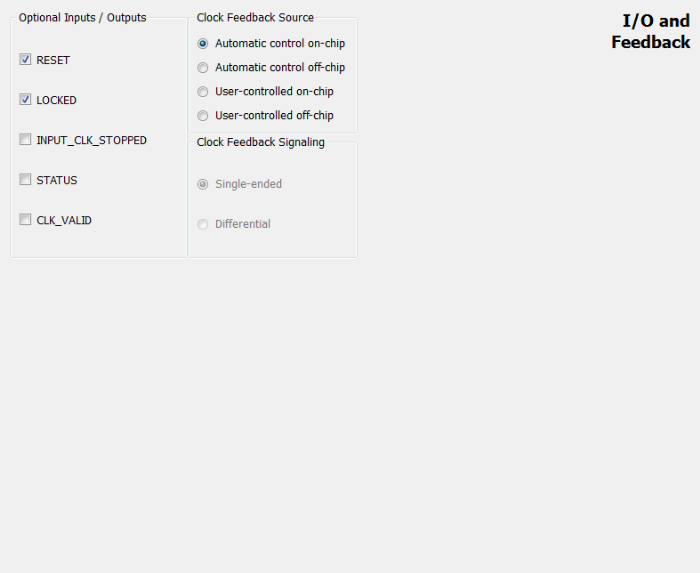

9:点击next,

10,点击next,直到finish。

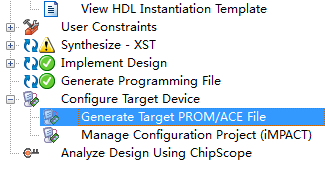

11:点击 dcm ip核,然后点击core generator前面的“+”号,双击View HDL Instantiation Template,在ISE 右侧窗口,可以看到例化该核的Verilog 语句。

12:继续添加 new source, verilog module 和 implementation constraint file。代码如下:

dcm_demo.v:

module dcm_demo( clk, rst, led_light ); input clk; input rst; output[7:0] led_light; wire clk_5m; dcm dcm( .CLK_IN1(clk), .CLK_OUT1(clk_5m), .RESET(!rst), .LOCKED() ); wire[7:0] led_light; led u( .clk(clk_5m), .rst(rst), .led(led_light) ); endmodule

Led.v:

module led(

clk,

rst,

led

);

input clk;

input rst;

output [7:0]led;

parameter T50M=5_000_000;

reg [26:0] count;

reg [7:0] led;

always @(posedge clk or negedge rst) begin

if (!rst) begin

count<=26'b0;

led<=8'b00000001;

end

else if (count==T50M) begin

count<=26'b0;

led<={led[6:0],led[7]};

end

else begin

count<=count+1'b1;

led<=led;

end

end

endmoduleDcm_demo.ucf:

Net clk LOC =P8 ; NET rst LOC =P7 ; NET "led_light<0>" LOC = M12; NET "led_light<1>" LOC = L12; NET "led_light<2>" LOC = L13; NET "led_light<3>" LOC = M14; NET "led_light<4>" LOC = R12; NET "led_light<5>" LOC = T12; NET "led_light<6>" LOC = T13; NET "led_light<7>" LOC = T14;

13: 右击project工程名, 点击 implement top module。

点击如图,产生bit文件并且通过仿真器 下载二进制文件到xilinx 芯片:

就可以看到led灯流起来了。如图: