.synopsys_dc.setup编写

0赞DC全称Design compiler,synopsys公司的综合工具,这综合EDA算这一家独大了。以自己的应用情况,写下自己基础使用。

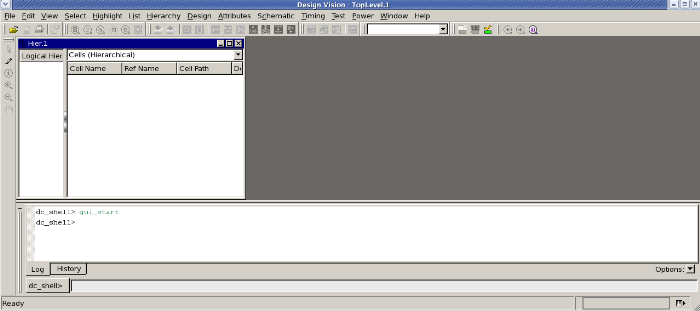

启动:

常用就是dc_shell或dc_shell–t,要想看GUI可以在启动上面后,输入gui_start,退出GUI输入stop_gui(并不退出DC)。GUI慎用,占用内存略多了些。启动后会在CWD下自动生成两个日志文件:command.log;view_command.log。在启动时可以添加tee命令,预防万一。如下:

dc_shell-t | tee dc_start.log &

#这样人为设置后会在启动时会生成一个dc_start.log的文件。在里面可以查看启动过程详细信息。后面的&,是使其在后台启动。即当前终端可继续进行其他操作,如不加在启动过程时不能在终端中进行其他操作。

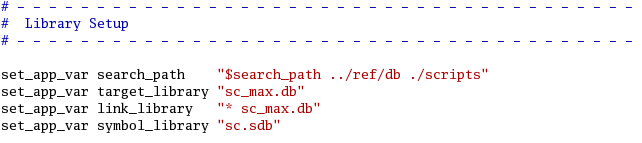

.synopsys_dc.setup文件解析与编写:

.synopsys_dc.setup文件在执行启动DC时会自动挂载(在启动DC时,请进入自己的工程目录下再进行启动,因为在DC工作过程中会生成较多的文件,也为了后面的操作更方便)。如果自己把setup文件修改为,其他名字了例如”.asd.setup”,那么启动DC时不会自动挂载。需要启动后自己source一下。

从上面启动画面可以setup文件里有search_path/target_library/link_library/

symbol_library/…….还有其他一些配置。以下面为例说明个部分作用

target_library/工艺库,有.db .lib两种格式,前一种为DC所用,打开看不懂~~,后面一种为人读所用。.lib可以转换为.db 此库主要描述了,工艺库中包含了各个门级单元的行为、引脚、面积以及时序信息(有的工艺库还有功耗方面的参数),DC在综合时就是根据target_library中给出的单元电路的延迟信息来计算路径的延迟。并根据各个单元延时、面积和驱动能力的不同选择合适的单元来优化电路。上面所说的计算,更多的是指用查找表来做。

link_library/ 链接库,这其中不仅包括target_library还包含工程加入的例如ip核等文件,*代表DC的内存区域(个人也说不清楚,加上就可以了)

symbol_library/此文件为使用GUI模式显示所用

search_path 就是告知DC如果上面那些命令没有加绝对路径,去哪里找

注意:在设置例如上面DC自带参数时,尽量使用set_app_var而不是set,更安全。例如前面那条命令如果你将target拼错,在读入setup文件时会报错。但是使用set时就不会目前报错,只有到最后出问题再去找就很难确定是哪里的问题。

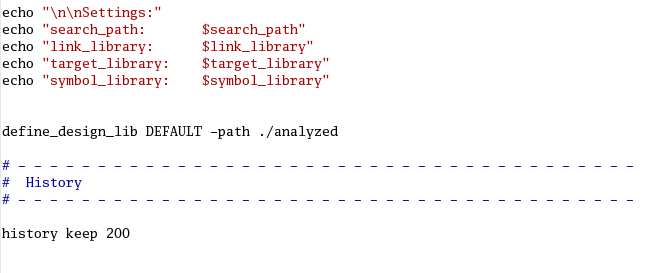

echo 打印命令,在启动时看到消息即执行此命令。

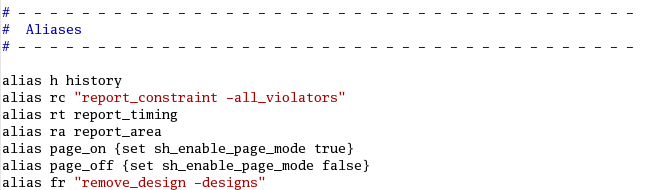

alias 设置简写命令

读入setup文件后可以使用printvar命令来进行进一步检查,路径设置信息。

可以使用alias查看所有简写命令。

如在dc_shell中使用linux的命令 先输入 sh 再输入命令。

现在即可以用read_verilog或者read_vhdl读入设计,成功读入后可以用list_design查看所读入文件和查看哪一个为TOP(也可current_design),默认读入的第一个文件为TOP。要设置为其他的文件为TOP,用current_design fsm.vhd 即可以从新设置。

此时可以用list_libs查看所用库信息。用check_design检查设计,会提示一些警告,可以根据情况忽略或者修改RTL级设计。

检查无误后,可用 write –format ddc –hier –output top.ddc 输出ddc文件,但是当RTL修改后需重新生成ddc文件。