SPARTAN6使用clock wizard产生多路输出时钟

0赞

项目上,需要产生高频的方波提供信号,但是实验室设备产生不了高频的,就想着用FPGA开发板产生一个高频的方波信号,由于开发板用的是SPARTAN6的主芯片,所以就想到了用DCM或者是PLL来产生。

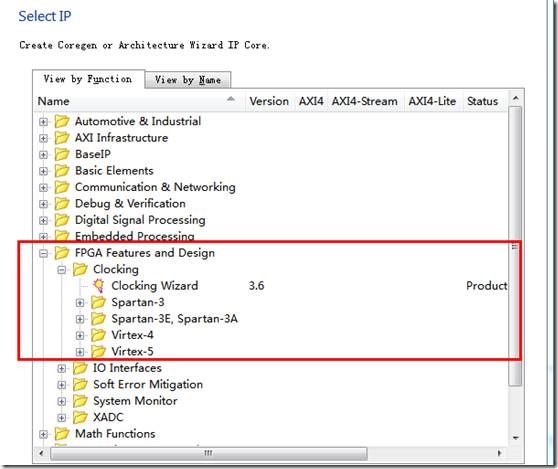

对于SPARTAN6来说,产生时钟用的是IP,所以需要使用CORE Generator来配置IP。添加新文件,然后选择IP,在右边填入IP名。

时钟的IP是在FPGA Features目录下的clocking里面,可以看到第一个clocking wizard不是灰色的,说明对于SPARTAN6来说,只有这一个IP是可以用的。后面可以发现,这个IP的功能很强大了,可以配置PLL和DCM。

选择该IP,就会弹出IP配置界面。这里,要注意的是在mode选项中,一定要选择manual selection。因为这样,配置出来输出时钟才是想要的时钟。因为在之前使用的是auto selection,结果发现输出的时钟和设置输出的时钟不一样。

选项有三个,推荐使用PLL和DCM_CLKGEN。因为这两个出来的时钟才是和配置的是一样的,使用第一个DCM_SP出来的时钟和配置的不一样。目前不知道原因是什么。

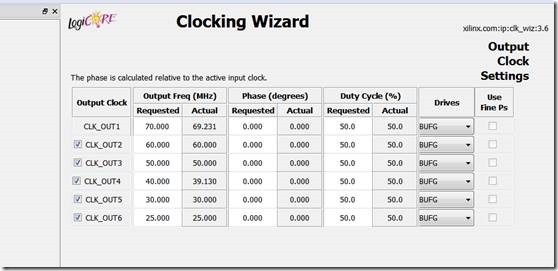

使用PLL_BASE,可以配置输出6个时钟,而使用DCM_CLKGEN可以配置输出3个时钟。因为我是要输出6个时钟,所以选择的是PLL_BASE。在下面的输入时钟填入50,表示输入的是50M的时钟。

第二页就是配置输出时钟。对于PLL_BASE可以最多选择6个输出,后面可以填入输出时钟的频率,对3栏对应实际的输出频率。后面的对应相位和占空比。

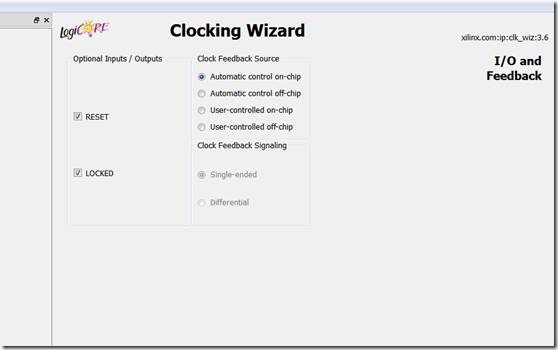

在下一页选择I/O和反馈。这里,使用默认配置,使用RESET和LOCKED管脚。RESET是复位管脚,高有效,所以要PLL正常工作的话,要为低电平。而LOCKED管脚是时钟锁定管脚,因为PLL的输出时钟是需要一定时间才会稳定的,当LOCKED管脚为高的时候,就说明输出时钟稳定了。反馈是为了给PLL内部使用的,这里使用默认配置。

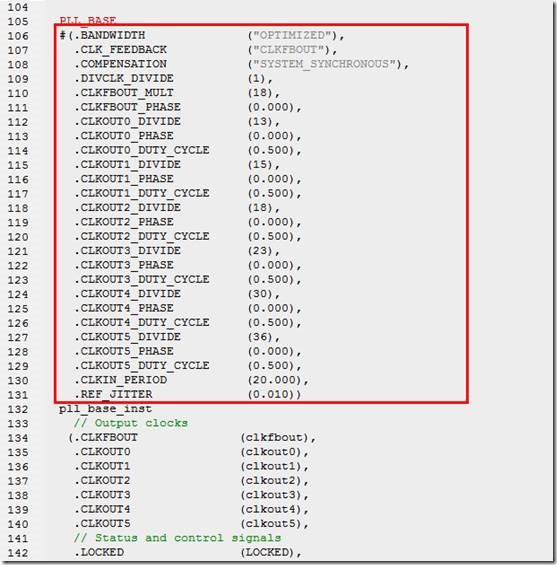

下一页是配置的参数,这些参数是在第二页配置输出频率,相位,占空比对应的参数。我们是可以修改这些参数的。

其实还可以发现,

输出的频率 = input clk * CLKFBOUT_MULT / CLKOUTx_DIVIDE(x为1-6),其实还要除以DIVCLK_DIVIDE,不过这里为1,就不用了。

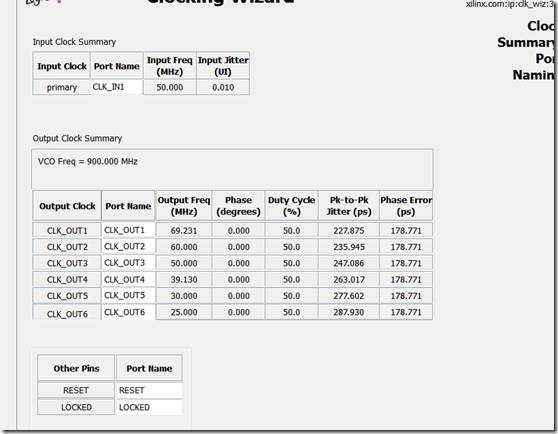

下一页就是时钟配置的信息了。

最后一页就是关于时钟IP的说明,配置的参数有哪些,会生成哪些文件。点击generate,就会生成IP了。

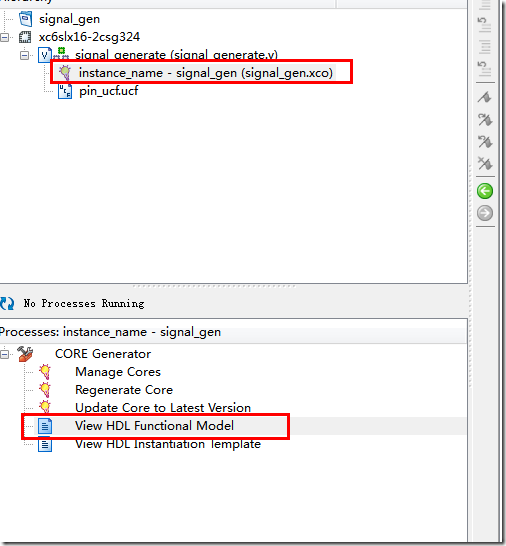

选择生成的IP,在选择下方的view HDL functional model,就可以看到生成的代码。

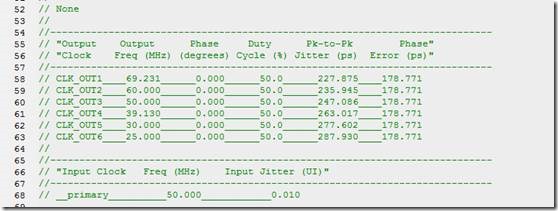

在注释中有说明,生成的时钟的频率,相位,占空比。

代码中,关键的是例化了一个PLL_BASE的模块,这个模块就是对应PLL。例化该模块的时候,填入了若干个参数,这些参数就是配置输出时钟用的,我们可以手动的去更改这些值,就可以得到想要输出的时钟,而不用在去IP配置界面去设置。

最后一步,分配管脚。使用PLL的输出时钟,我记得是有专门的管脚与之对应的。但是我使用的是普通管脚,如果直接将普通管脚给分配到PLL的输出时钟上,implement的时候,就会报错,所以为了强制让PLL的输出时钟能够分配到普通管脚上,需要在分配管脚的时候加一个命令。

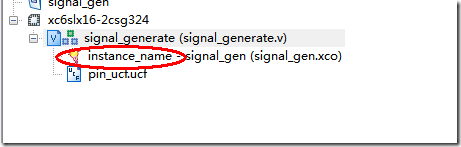

其中instance_name是你例化PLL的模块名,在顶层中,我例化的该PLL模块的名字是instance_name。所以这里就是instance_name,后面的都是固定的。

这样,就可以implement了。

我生成bit流下到开发板后,用示波器去看输出波形,发现输出的高频率时钟的波形就很不理想了,已经接近正弦波了。所以还是不推荐将PLL的输出连接到普通管脚上。