dds学习

0赞目前dds,用来产生信号是比较普遍的方法。dds是数字频率合成,利用数字的器件,加上da就可以产生模拟需要的正弦波,三角波,方波波形。

对于一个模拟正弦信号sin(t+a)。实际上,t的值是一个模拟量,0到2π(以一个周期考虑),但是我们也可以这样考虑。t的值是从0通过一个很小的间隔到deltaT递增到2π。如果deltaT的值较小,那么函数变化就比较慢,从而信号频率就比较小。但是如果deltaT的值较大,那么函数变化就很快,从而信号频率就比较大。因此我们可以将sin(t+a)将之在0到2π采样很多值,然后将这些值存在一个rom里面。然后将t当成是这rom的地址,通过改变地址,得到不同的sin(t+a)的值。然后改变rom地址的变化速度,那么就可以实现改变sin(t+a)的频率了。

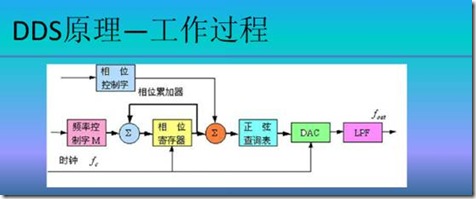

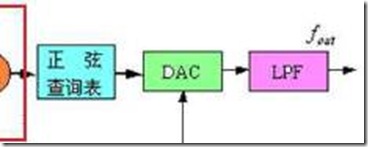

dds原理如下所示:

dds的主要原理是通过查表的方式确定输出。将波形的一个周期的数据存储在一个rom里面,然后在根据不同时间改变rom的地址值,在将rom输出的值通过da转换,那么就会得到不同频率的模拟波形。

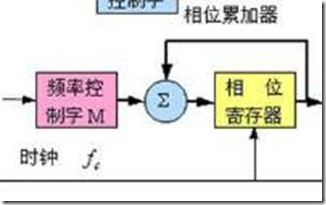

对于第一部分,频率控制:

这部分主要是确定输出信号的频率的。通过预置不同的频率控制字M,那么加到后面的rom的地址值就会按照该频率控制字M递增。就会调整输出波形的快慢。M较小,rom的地址就会增加得比较慢,那么rom输出的值就变化的慢,那么输出的波形,频率就低。M较大,rom的地址就会增加得比较快,那么rom输出的值就变化得快,那么输出的波形,频率就高。

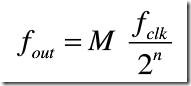

fclk是时钟的频率,n是rom的地址位数。fout是输出频率。

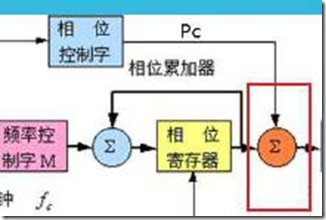

第二个部分,相位控制:

图中的第二个累加器部分。该部分是相位控制部分,用于调整输出波形的相位。这个相位值可以理解为sin(t+a)中的a。

第三部分就是输出值

从前面的电路得到了rom的地址,将该地址直接接到rom,就可以从rom里面读取值,然后将该值通过DA,转换为模拟值。在通过一个低通滤波器,就是我们所要的输出波形了。

以上,是考虑的正弦信号,其实只要将rom里面的值存为其他波形的值,那么输出的波形就是对应的波形,只是频率不同而已了。

可以看出用dds产生波形,是比较容易的,用的都是数字器件,好控制。但是要注意输出的波的频率不能太高,即频率控制字M的值不能太大,否则输出的波形会失真。一般输出的波形频率为时钟的30%-40%。

之后,我们就要用FPGA来实现dds了。