Verilog中inout的使用

0赞这两天在做verilog的ds1302,ds1302中有一个端口是输入/输出管教。即这个管教即是输出,同时也可以当输入。在verilog中有一个特殊的端口与之对应,就是inout。

Inout这个端口,之前用得不多,所以用法也不怎么记得。但是这个地方要用,所以就要学习下。

在端口申明中,可以申明一个端口为inout,申明后,这个端口就是输入/输出端口。那么怎么用这个端口了,什么时候让他输出,什么时候让他输入。这个时候,就有一个固定的用法。就是assign

如:申明一个 inout端口 a, inout a,

那么在用的时候,就要这样用: assign a = read == 1 ? 1'bz : data;

可以看出,这里多了一个read信号,这个read信号就说明此端口a,在什么时候作为输入,什么时候作为输出。当read为1的时候,a为输入,否则作为输出。

以下是一个inout使用的一个实例代码:

module inout_1( input clk, input rst_n, input read, input data, inout a, output reg b ); assign a = read == 1 ? 1'bz : data; always@( posedge clk ) begin if( !rst_n ) b <= 0; else begin if(read) b <= a; end end endmodule

以上代码,功能是,当a端口作为输入的时候,把输入a的值给输出b。当a端口作为输出的时候,将输入data的值输出给a。

Inout使用时很简单的,其实就是控制使能信号。使能信号有效的话,就将端口当做输入用。使能信号无效的时候,就把端口当做输出,此时改变输出的值,就改变assing语句中的输出信号值(上例中就是data信号)。、

接下来就是仿真了,对于inout的端口,仿真和其他两种端口是不一样的,input端口在仿真中,就是定义为reg型,然后直接在测试文件中改变值。而输出就是定义为wire型,直接在仿真结果中查看信号结果即可。

那对于inout又该怎么定义信号了。其实inout信号,在测试文件中,要定义为wire型。另外还要加一个assign语句。

如上例中,a为inout信号,那么在测试文件中,要有这样一个语句

assign a = read == 1 ? in_a : 1'bz;

信号in_a是a的输入值,可以看出,测试的assign和功能代码中的assign顺序是反着的。在功能代码中,是使能信号有效的时候,inout信号的值为z,即表示为输入。但是在测试中,信号有效的时候,inout的值是定义的一个输入的值,而信号无效的时候,值为z,表示输出。

上面的顺序不能反,之前做的时候,在testbench中对assign的赋值顺利反了,结果仿真中,a的值输出的时候有值,而输入的值为高阻。

以下是上面功能代码的测试代码:

module inout_1_tb;

// Inputs

reg clk;

reg rst_n;

reg read;

reg data;

// Outputs

wire b;

// Bidirs

wire a;

// Instantiate the Unit Under Test (UUT)

inout_1 uut (

.clk(clk),

.rst_n(rst_n),

.read(read),

.data(data),

.a(a),

.b(b)

);

reg in_a;

assign a = read == 1 ? in_a : 1'bz;

always #1 clk = ~clk;

initial begin

// Initialize Inputs

clk = 0;

rst_n = 0;

read = 0;

data = 0;

in_a = 0;

#10 rst_n = 1;

repeat(10) begin //a作为输出 此时a的值等于data

#2 data = {$random}%2;

end

read = 1;

repeat(10) begin //a作为输入,此时a的值为in_a

#2 in_a = {$random}%2;

end

// Add stimulus here

end

endmodule

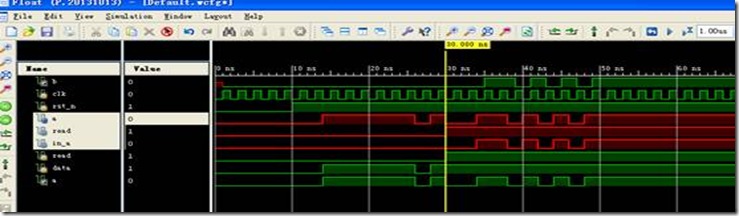

用isim仿真,其仿真图如下:

从图中,可以看出,当read信号为低的时候,a作为输出,此时a的值等于data的值。当read信号为高的时候,a作为输入,此时a的值等于in_a的值。仿真正确。

对于inout信号的时候,要注意使能信号的正确运用,以及对应的assign赋值写好。其次要注意,inout信号最好是使用在设计的端口中,不要在设计的内部模块中使用inout。