nios2之LCD硬件设计

0赞最近手边有了DE2-115开发板,就用来玩玩nios2,顺便学习一个altera的开发流程,因为之前都是在用xilinx的。

玩了之后,确实nios2的功能很强大,但是这开发的软件很不好用,有时候会出莫名其妙的问题,搞得很蛋疼。

以下实现一个流水灯和LCD1602显示。流水灯通过按键来控制,按键通过外部中断检测。

新建工程:

第一个是工程的路径,该路径不能有中文和空格。

第二个是工程的名字,也是不能有中文和空格,

第三个是顶层设计的名字,也不能有中文和空格。

下面一页选项是选择添加的文件,这里不需要添加文件。如果需要在工程中加入文件,可以再这里加入。

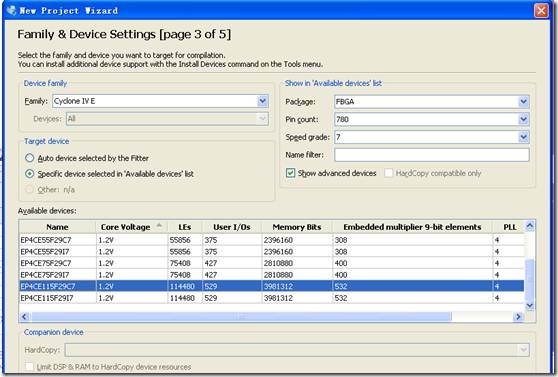

下面这一页是选择器件,如果你是要把设计下到altera FPGA芯片中的话,这里的器件不能随便选择,要选择你对应的器件,否则是下载不成功的。

这里我用的是de2-115,用的器件是EP4CE115F29C7。看这芯片,就知道这芯片挺好的。表中还有对芯片的一些性能描述。可以看到merory有3981312bit,也就是486kb。还是挺大的。

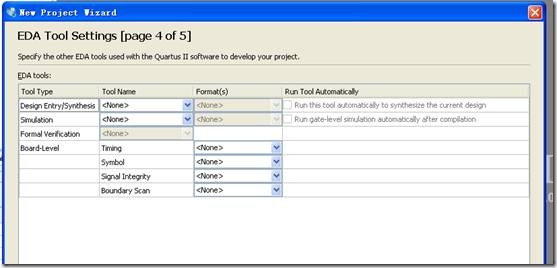

这里是选择EDA功能。Quartus可以使用第三方工具,但是使用的时候,是需要配置的,这里就是配置的。我们不需要,直接跳过。

最后一个就是功能的信息。直接finish,就建立工程了。

这样,功能就建好了,首先是新建一个原理图。用原理图开发nios是比较方便的,而且不容易出错。

在将原理图保存为lcd。这里注意要将原理图保存为lcd,因为之前设置的顶层是lcd,而顶层的名字要和顶层文件的名字要一样,才能被综合和布局布线的。如果这里保存的名字不是lcd的话,那么就要在工程中将原理图设置为顶层。

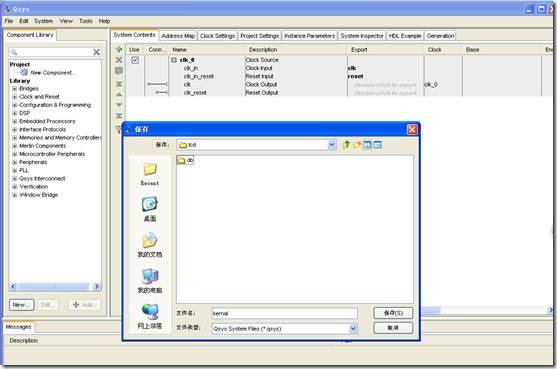

然后,打开qsys,进行nios2硬件开发。对于quartus后面出的版本,已经用qsys替代了sopc builder。

首先,还是保存qsys。保存是个好习惯。

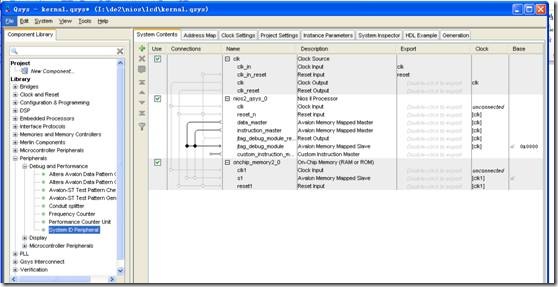

然后就开始我们的qsys硬件设计了。

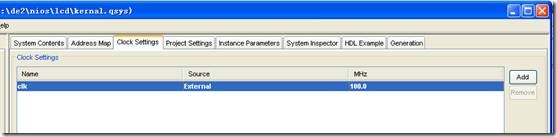

首先,我们要先改下时钟。可以看到在界面中有一个clk_0,这个是默认的50M时钟,我们知道一个嵌入式系统肯定是需要一个时钟的,这个时钟就可以当系统时钟用,但是有时候,一个系统需要的不止一个时钟,那么就可以添加时钟。

在clock setting中设置。这里只用到一个时钟,把时钟名字改为clk,频率改为100M。如果需要其他时钟,可以点击Add按钮,添加时钟。

时钟设置好后,就要添加CPU了。因为一个嵌入式系统,是需要一个处理器的。

选择左边的nios2.这个nios2是altera的32位处理器软核。大家可以理解为一个32位的单片机。

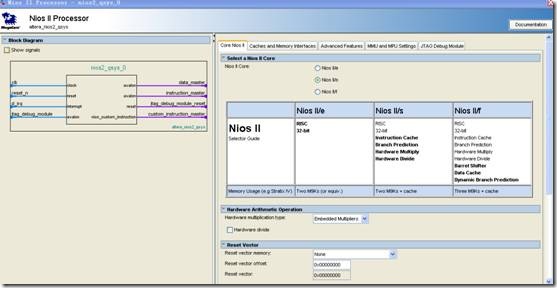

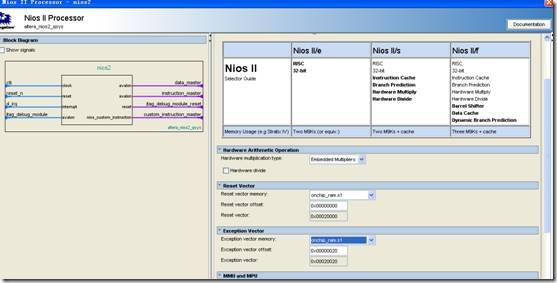

出现配置界面,这里是对nios2的配置。Nios2有三种核,关于这三种核可自行百度,这里选择的是第二个。其他的默认。直接finish。

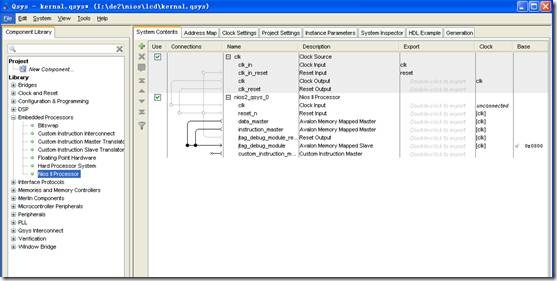

然后就可以看到nios2添加进去了,可以看到是没有连线的,qsys中的IP互联线是需要自己手动连接的。这里先不用管。

然后是添加ram。Ram是一个嵌入式处理器必须的东西,可以存储程序,可以存储数据。这里简单起见,使用的是芯片内部的ram,没有用外部的SDRAM和SRAM。

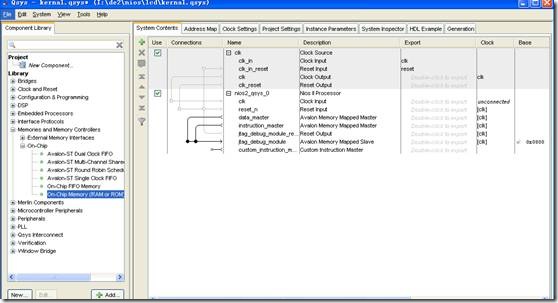

选择左边的on-chip memory。

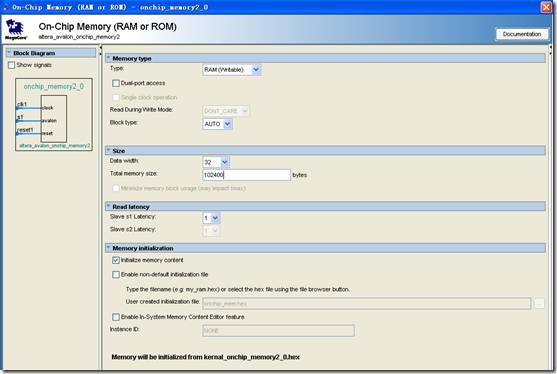

在配置界面把大小改为102400,即100K。这个大小够我们写一些简单的程序了,这里注意,这大小不是随便设置的,要小于芯片提供的ram大小。之前选择芯片的时候看过,该芯片的ram大小为486k,所以大小要选择比这个小。

这个时候,就多了一个onchip-ram。我们这里会把这个ram当做数据和指令存储器。

然后添加system id。这个system id也是必须的,就是用来标示该设计的CPU的。就直接添加就好了

在配置界面,可以给ID改个其他数字。

添加后,界面就变成下面这个样子了。

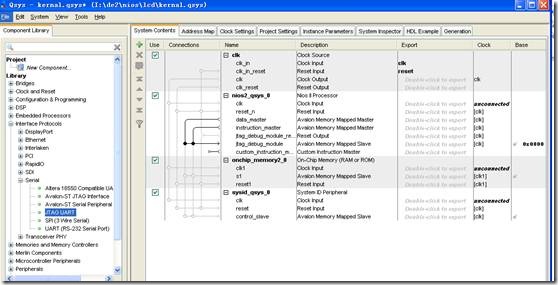

然后添加jtag-uart。这个jtag-uart是用来向PC机传送信息的。只是用的是jtag,而不是串口。

直接默认配置,finish。

界面就变成上面这个样子了。

这下,一个nios2最小系统就构建好了。不过这个最小系统能干的事就比较少了,就只能发送数据和接收数据。

接下来,就要添加我们需要用的外设了。

首先是添加输出IO。因为我们要控制led。在nios2中,对于输入输出IO,都是用PIO的IP核。

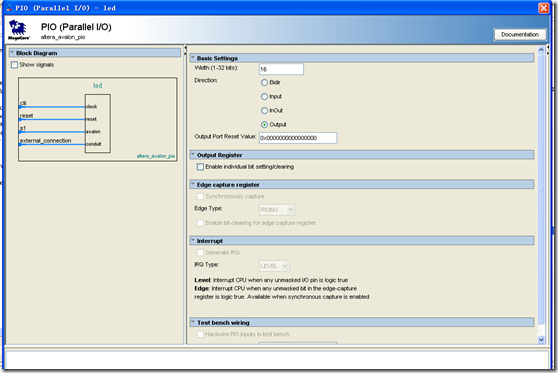

在配置界面,需要配置PIO的输入输出。这里IO是用来控制16个led,所以输出宽度设置为16,方向设置为输出,复位值设置为0。下面的不选择。Output register是表示能单独的对每一位清零或置位,就相当于stm32的IO位操作。这里不选择。因为是输出,所以中断和边缘检测是不能使用的。

这样界面就多了一个PIO。

然后添加按键的PIO。还是添加PIO,不过配置要改一改。

因为是一个按键输入,所以宽度设置为1.方向设置为输入。当设置为输入,可以看到下面边缘检测和中断使能了。因为用中断方式检测按键,所以中断要打开,方式设置为电平。如果中断方式要设置为边沿的话,那么要打开边缘检测。

设置好后,直接finish。

界面就又多了一个PIO。

其实就是你添加一个IP,界面就多一个IP。

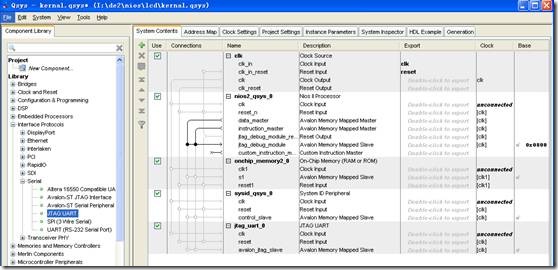

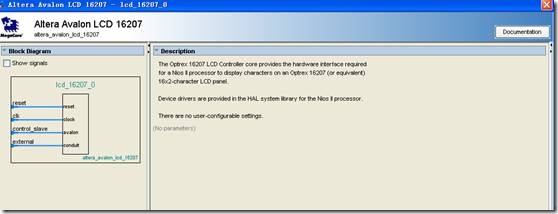

剩下就添加lcd了。以前我们驱动lcd的时候,都是自己写代码,去驱动lcd。但是altera比较人性化,把驱动的部分做成一个IP,我们直接调用使用就行了。

这个IP,没有配置信息,就是不用配置。直接finish,

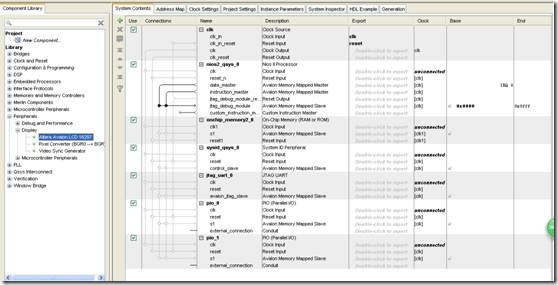

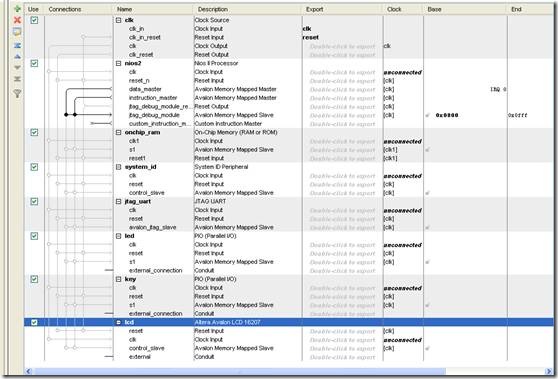

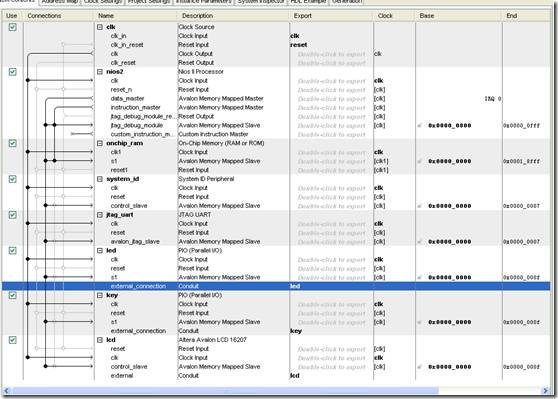

这样,就完成了模块的添加。接下来,就对模块重命名和连线了。

重命名后,可以看到,从名字就可以看出该模块的功能是什么了。

然后就开始连线了。连线这个,第一次连的时候,不知道怎么连,但是多连几次,就知道怎么连了。

首先clk,每个模块都有一个clk,因为这里只有一个时钟,所以模块的时钟都和clk的时钟连在一起。但是如果有多个时钟,就要注意,每个模块要连相对应的时钟。

然后是连数据总线和指令总线。这个的一般连法是,如果是ram,flash,那么数据总线和指令总线都要和nios2相连。对于其他的,只要连数据总线就行了。

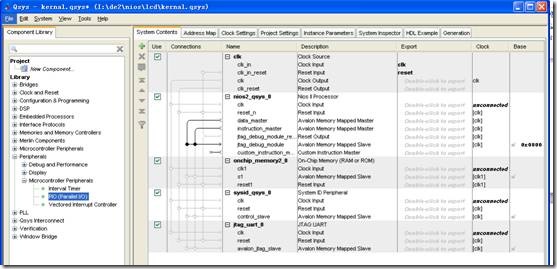

然后是将模块的输出导出。有些模块的输出是需要导出的,比如led,key,lcd,因为这些模块需要将管脚导出到对应的外设上面控制,才能控制响应的外设。

这个直接在模块的external那一行的export那一列,双击就行了,然后改改名字就导出了。时钟和复位是默认导出的。

最后就是复位的连线了。

如果整个系统只有一个复位的话,那就简单了,直接选择

这样,就将所有的复位都连起来了,但是如果系统不是只有一个复位,那么就要自己连了,模块连对应的复位管脚。

这样,就完成了整个的硬件设计了。接下来在做一些设置就行了。

其实可以看出,qsys完成的功能就相当于我们自己去设计一个嵌入式系统,首先,系统需要什么外设和CPU,然后找来,然后开始连线,CPU和外设是怎么相连的。只不过在qsys中这个过程就简化了,只需要去调用IP,然后连接就可以了。

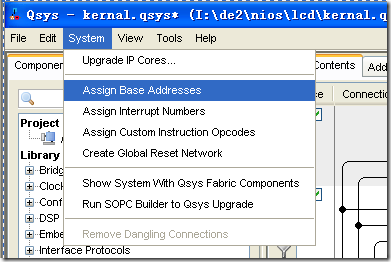

接下来,要给每个外设分配地址。可能很多人有疑问,这个外设的地址到底是用来干什么的。

其实在嵌入式系统中,外设是通过寄存器来进行访问的,比如说对应IO,IO可以输入可以输出,那么肯定就要有一个寄存器来控制IO的方向,那么这个寄存器总要有个地址吧,这样CPU才能访问到。于是IO有了一个方向寄存器的地址。我们要IO输出的时候,怎么输出啊,就是向IO数据寄存器写数据啊,这样IO就输出我们想要的东西了,于是总要有个寄存器来做这个功能吧,那这个寄存器也要有个地址吧。这样我们的IO就有两个寄存器地址了。把IO的功能寄存器集合起来,那是不是就有一个地址范围了。为了方便管理,这些寄存器的地址都是在一个连续的区域,这样我们就好控制了,就可以用指针去操作这些寄存器,就相当于操作IO了。

所以需要给外设分配地址,当然这分配地址我们交给软件来分配。直接

这样,就分配好了地址了。

然后,还要设置下nios2的复位地址和异常地址。

在nios2软核中设置复位向量和异常向量都指向onchip_ram。

最后是分配下中断号就行了。

在有中断的地方的IRQ列双击就行了,这样就为需要中断的外设分配一个中断号。有了中断号,才能写程序的时候注册中断号,中断才能用。

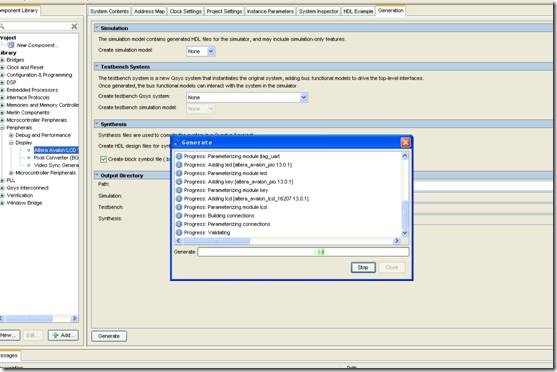

以上完成后,就完成了硬件设计了。然后

Generate就行了。这样就完成了qsys设计了。

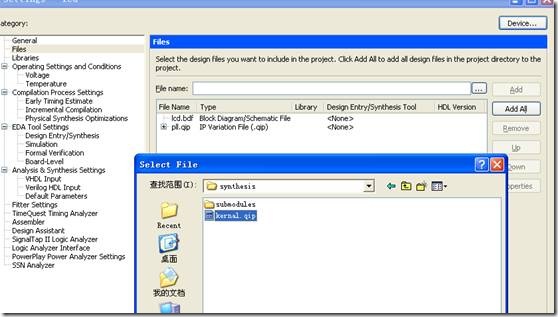

剩下,就将生成的qsys设计导入到quartus。

在原理图顶层中导入qsys,另外导入一个pll,pll的输出时钟频率是100M,这个时钟就是我们的nios2的系统时钟。然后对管脚进行分配。然后把kernal的.qip文件加入到工程中,不然编译的时候会报错。

这里要注意的是,按键的输入要接一个非门,因为nios中断对高电平敏感,而按键的输入平时就是高电平,按下才是低电平,所以这里要取反,不然就一直进入到中断里面去了。

然后就是漫长的编译过程了。

编译完成后,将生成的sof文件下到芯片就行了,这样,就完成了硬件设计了。。剩下就要进行软件设计了。