cortex-a8裸机系列: 第二章 S5PV210的简单介绍

1赞

一、 s5pv210的流水线

为增加处理器指令流的速度,ARM使用多级流水线。S5PV210是13级流水线,ARM11为8级。

下图是执行过程。

PC指向正被取指的指令,而非正在执行的指令。因为在armv7架构的cpu中,是可以操作PC的,如果在一个时刻读取PC的指,那么当前读取PC的指令所在的地址就是PC-8。

在armv8的64位架构中,不允许对PC进行操作。

二、 ARM的异常处理机制

1. 异常产生

当异常产生时,ARM core:

拷贝CPSR到SPSR_<mode>

设置适当的CPSR

改变处理器模式进入ARM态

改变处理器模式进入相应的异常模式

设置中断禁止位禁止相应中断

保存返回地址到LR_<mode>

设置PC为相应的异常向量

返回时,异常处理需要

从SPSR_<mode>恢复SPSR(恢复的时候,就从ARM状态跳回到THUMB2状态)

从LR_<mode>恢复PC

以上操作只能在ARM态下执行,也就在异常产生后,会将CPU的状态设置为ARM状态。

异常处理中有一些事硬件自动做的,有一些是软件做的。

硬件做的事有:保存CPSR, 保存返回地址,设置CPSR。PC设置为异常表的入口地址。

软件做的事有:保存寄存器,执行异常处理程序。

2. 异常向量表

ARM的CPU实现异常都是通过异常向量表来实现的。即每一个异常,都有对应的异常向量表的入口地址,当异常产生后,会自动跳转到异常向量表的入口地址处。

复位,软中断,中断,快速中断,取指令异常、数据异常等,统一称为异常。所以说,中断其实是异常的一种。

异常的定义就是突发事件,打断了CPU的正常常规任务,CPU不得不跳转到异常向量表中去执行异常处理程序;中断是异常的一种,一般特指SOC内的内部外设产生的打断SOC常规业务(串口中断),或者外部中断(SOC的GPIO引脚回来的中断)。

异常向量表处理:

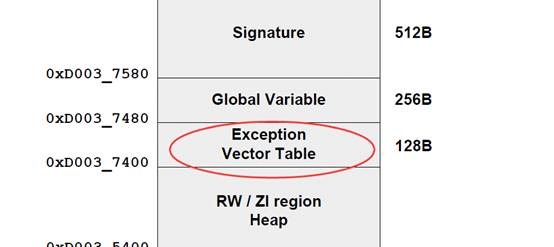

210的异常向量表的起始地址可以通过设置进行改变(CP15协处理器中设置),以适应操作系统的需求。但是在系统刚上电启动时,210内部的BL0程序在IRAM中设置了异常向量表,供暂时性使用。

通过手册可知,异常向量表的起始地址是0xd003_7400。知道了异常向量表的起始地址,则各个异常的入口地址都知道了。

使用宏定义定义各个异常向量的地址。

分别编写对应异常处理函数,其实就是往异常向量表中写入对应异常处理函数的地址。可见,当异常产生的时候,硬件会从对应异常向量中取出跳转地址值给PC,然后程序跳转,执行对应异常处理函数了。这个和STM32很类似了,和ARM11就不一样了。

函数名的本质是函数的首地址

1. 函数名在C语言中的理解方法和变量名其实没区别。编译器会把这个函数的函数体对应的代码段和这个函数的函数名(实质是符号)对应起来,等我们在使用这个函数名符号时,编译器会将函数的函数体实际上做替换。因为函数体都不止4个字节,而函数名这个符号只能对应1个地址,所以实际对应的是函数体那一个代码段的首地址。

2. 拿C语言中的语法来说,函数名就是这个函数的函数指针。

将异常处理程序的首地址和异常向量表绑定起来后,异常处理初步阶段就完成了。因此在异常产生后,硬件自动跳转到对应异常向量入口区执行,就可以执行事先绑定好的异常处理函数。

中断处理要在汇编中处理

1. 中断处理要保护现场(中断从SVC模式来,则保存SVC模式下的必要寄存器的值)和恢复现场(中断处理完成后,准备返回SVC模式前,要将保存的SVC模式下的必要寄存器的值恢复回去,不然到了SVC模式后寄存器的值变了,SVC模式下原来正在运行的任务环境就被破坏了)

2. 保护现场包括:第一:设置IRQ栈, 第二:保存LR , 第三: 保存R0-R12

3. 为什么要保存LR寄存器?中断返回时关键的2个寄存器就是LR和CPSR。所以在进入IRQ模式时,应该将之前模式的下一句指令(中断返回地址,被硬件自动保存在LR寄存器中)和CPSR保存起来,因为异常处理程序,很有可能会修改这两个寄存器的之。因此要事先保存,将来恢复的时候,才可以把中断返回地址给PC,CPSR复原。

4. 中断返回地址保存在LR中,CPSR保存在SPSR中。这些操作都是自动的。

5. 使用栈来保存寄存器

中断处理,汇编编写

通过stmfd来保存寄存器,通过ldmfd来恢复寄存器。并返回。

三、 协处理器CP15

ARM的协处理器,是比较重要的,特别是这CP15,可以控制很多东西。如MMU,icache,dcache等。

协处理,通过mcr 和mrc指令来进行访问。

mrc用于读取CP15的寄存器

mcr用于写入CP15的寄存器

协处理器

l SOC内部另一处理核心,协助CPU实现某些功能,被主CPU调用执行一定任务

l ARM设计上支持多达16个协处理器,但是一般SOC只实现其中的CP15

l 协处理器和MMU,CACHE,TBL等处理有关,功能上和操作系统的虚拟地址映射、cache管理等有关

• mcr{<cond>} p15, <opcode_1>, <Rd>, <Crn>, <Crm>, {<opcode_2>}

• opcode_1:对于cp15永远为0

• Rd:ARM的普通寄存器

• Crn:cp15的寄存器,合法值是c0~c15

• Crm:cp15的寄存器,一般均设为c0

• opcode_2:一般省略或为0

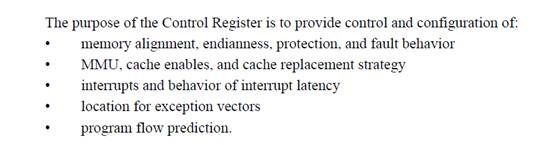

对于C1寄存器,

要想使用ARM模式下的异常,30位是要置0的。而当这一位为1的时候,在ARM模式下,是进入不了一场模式的,因此就造成中断是不起作用的。

ARM处理器工作模式

ARM有7个基本工作模式

1. User: 用户模式,大部分任务执行在这种模式

2. FIQ: 快速中断模式

3. IRQ: 中断模式

4. SUPERVISOR: 复位和软中断的时候会进入这种模式

5. Abort: 存取异常

6. Undef: 执行未定义指令会进入这种模式

7. System: 使用和User模式相同寄存器集的特权模式,操作系统模式,操作系统内核工作在这个模式下。

除USER模式是normal外(这个模式也是linux中用户的模式),其他都是privilege模式

各种模式下权限和可以访问的寄存器不同

CPU是硬件,OS是软件,软件的设计要依赖硬件的特性,硬件的设计要考虑软件需要,便于实现软件特性。

操作系统有安全级别要求,因此CPU设计多种模式是为了方便操作系统的多种角色安全等级需要。

这些模式在操作系统的时候用处才比较明显。如果只是裸机开发,模式的用处都不大。

以上是跟着朱有鹏大神学习的总结。