cortex-a8裸机系列:第八章 DRAM

0赞一、 SDRAM引入

SDRAM特性:

容量大,价格低,掉电易失性,随机读写,总线式访问。

SDRAM/DDR都属于动态内存(相对于静态内存SRAM),都需要初始化才能使用,不像SRAM开机上电后就可以直接运行。

SDRAM在系统中属于SOC外接设备。SDRAM通过地址总线和数据总线接口(总线接口)与cpu通信。

二、 x210-v3的SDRAM芯片

开发板原理图上使用的是K4T1G164QQ,但实际开发板上用的是另一款N2TU161666-AC,不过两个是完全兼容的。

全球做SDRAM的厂商不多,二线厂家做的产生参数都是向一线厂家(三星、kingston)看齐,目的是兼容一线厂家的设计,然后让在意成本的厂商选择它的内存芯片替代一线厂家的内存芯片。

SDRAM的这个市场特征就导致了这个东西比较标准化,大部分时候细节参数官方(芯片原厂家)都提供一个参考值。

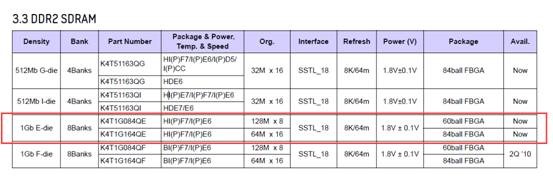

K4T1G164QQ:

K表示三星产品。

4表示是DRAM。

T表示产品号码(DDR2 SDRAM)。

1G表示容量(1Gb,以bit为单位,等于128MB,开发板上一共用了4片相同的内存,总容量是128*4=512MB)。

16表示单芯片是16位宽的。

4表示8bank。

Q表示SSTL_18(1.8V,1.8V)。

三星官方提供的数据手册上其实没有芯片相关的参数设置信息,都是芯片选型与外观封装方面的信息,选型是给产品经理来看的,封装和电压等信息是给硬件工程师看的。软件工程师最关注的是工作参数信息,而这些参数信息,官方会提供参考代码。

三、 s5pv210的memory port

对于CPU,CPU是通过片上的memory port和外部的SDRAM芯片进行通信的。对于s5pv210,有专用的和SDRAM芯片通信的memory port。

1. memory port

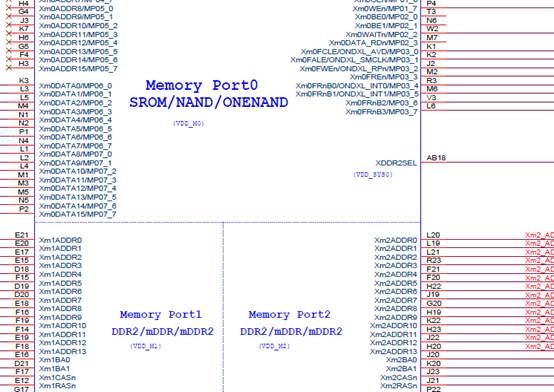

210上面有3部分的memory port。

可以看出,对于memory port0,可以接SROM/NAND/ONENAND。对应是Xm0xxx的管脚。

对于memory port1、2,可以接DDR2,mDDR,mDDR2。对应Xm1xxxx,Xm2xxx的管脚。

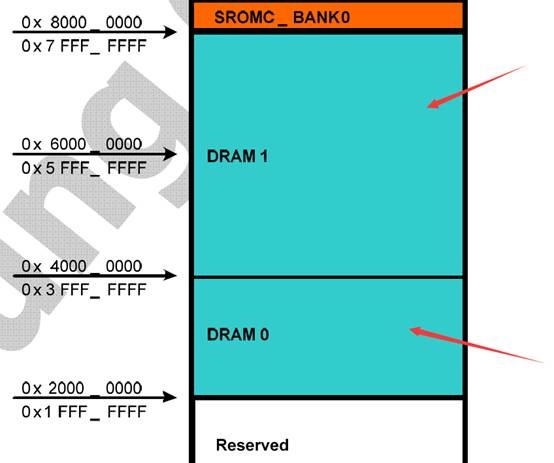

2. DRMA0和DRAM1

210共有两个内存端口(好像是有两个内存插槽)。再结合查阅数据手册中内存映射部分,可知,两个内存端口分别叫DRAM0和DRAM1。

对于DRAM0,内存地址范围: 0x2000_0000 – 0x3fff_ffff。512MB大小

对应原理图上的引脚是 xm1xxxx

对于DRAM1,内存地址范围: 0x4000_0000 – 0x7fff_ffff。1024MB大小。

对应原理图上的引脚是 xm2xxxx

3. 结论

1) 整个210最多可以支持内存1.5GB。如果给210更多的内存,CPU是无法识别的。

2) 210最多支持1.5GB内存大小,但是实际的开发板不一定要这么多,比如x210开发板就只有512MB内存大小。连接方法是在DRAM0端口分布了256MB,在DRAM1端口分布了256MB。

3) 由2可知,x210开发板上内存合法地址是:

0x2000_0000 – 0x2fff_ffff(256MB)

0x4000_0000 — 0x4fff_ffff(256MB)

当板子上DDR2初始化完成之后,这些地址都是可以使用的;如果使用了其他的地址,就会出现内存读取异常,就出现错误了。

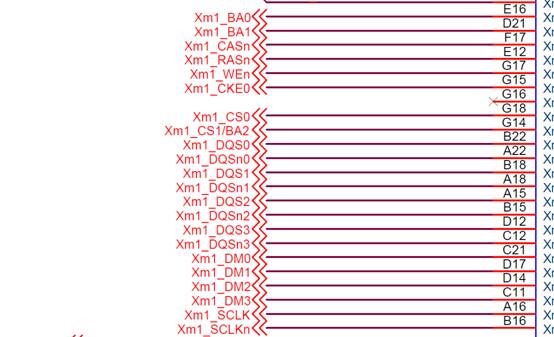

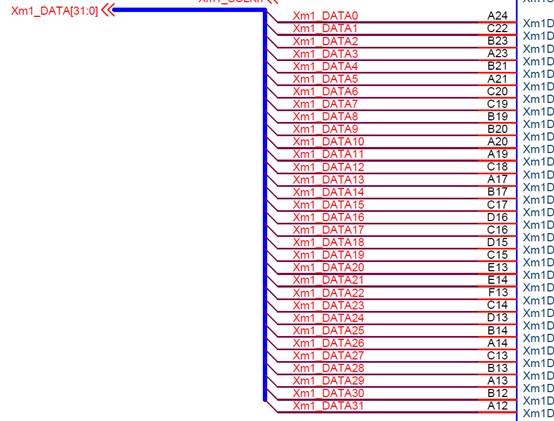

四、 X210-v3的DRAM的原理图

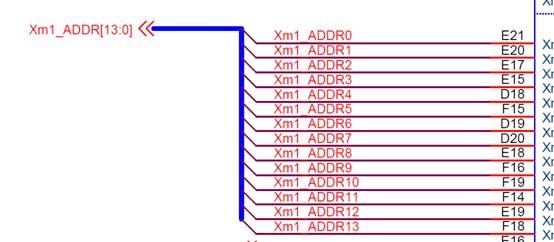

原理图上,地址线有14根,这个地址线的位宽是和DRAM芯片的数据手册对应的。

控制信号

数据线32根,表示数据访问是以32位为单位访问的。

以上就是xm1的部分,还有xm2的部分,信号线是一样的。

五、 SDRAM结构

X210使用了4片内存(每片1GB,128MB)。每片内存的数据总线都是16位的。每两片使用一个DRAM区域。这样,就相当于一片256MB大小的32位DRAM芯片。

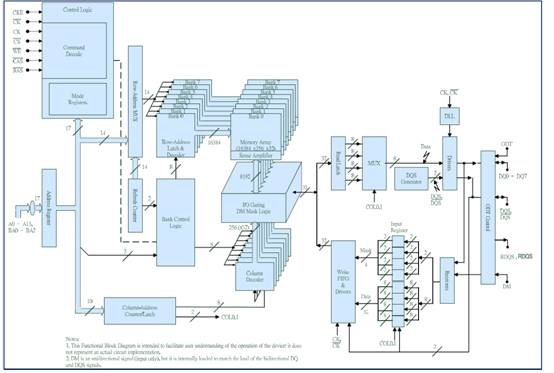

SDRAM结构框图:

128Mb * 8 8指的是8个bank

输入BA0-BA2选择8个bank中的一个bank

一个bank有128Mb,通过row address + column address的方式综合寻址。

Row address 14位

Column 10位

一共能寻址的范围是: 2的14次方 + 2的10次方 = 2的24次方,就是16MB内存,也就是128Mb内存,这个大小也就是一个bank的大小。所以8个bank,总大小就是16*8=128MB。

初始化DDR2

DDR初始化和SOC(准确的说是和SOC中的DDR控制器)有关,也和开发板使用的DDR芯片有关,和开发板设计时DDR的连接方式也有关。

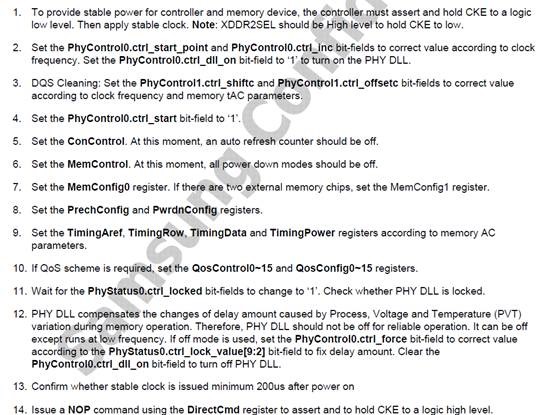

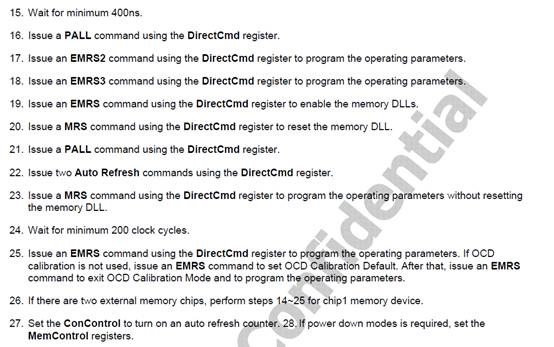

初始化步骤,27步(s5pv210数据手册598):

因为x210内存连接了两个,DRAM0控制器和DRAM1控制器,所以初始化需要两次,一次初始化DRAM0,一次初始化DRAM1。

六、 DRAM控制器

CPU不会直接操作memory port去和外部的DRAM芯片通信,而是去操作CPU内部的DRAM控制器来和外部的DRAM芯片通信。

DRAM的作用,就是CPU和外部DRAM芯片的桥梁,使之能相互进行通信。CPU通过AXI总线,可以直接对DRAM的地址进行读取。而忽略掉DRAM的接口复杂的时序。

1. s5pv210的DRAM控制器

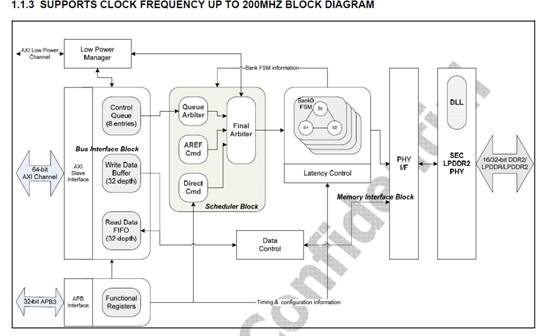

DRAM控制器使用SEC DDR PHY接口。

s5pv210拥有两个DRAM控制器,DRAM0,DRAM1。其中DRAM0最大支持512MB,DRAM1最大支持1GB。但是两个控制器如果同时使用的话,只能驱动同一类型的存储器。

DRAM的关键特性

l 兼容JEDEC DDR2,低功耗DDR和低功耗DDR2

l 使用SEC LPDDR2 PHY接口,支持高速存储设备

l 支持最大2个chip选择,每个chip为1/2/4/8 bank

l 支持128Mb,256Mb,512Mb,1Gb,2Gb,4Gb密度的存储设备

l 支持16/32位的数据位宽

l 优化的流水线,实现低latency

l 支持QoS策略,保证在某些应用下的低latency

l 先进的嵌入式调度程序

l 支持 chip/bank 交互 和存储中断

l 支持AMBA的AXI

l 采用可变的低功耗策略,减少动态和静态电流

l 支持外部访问

l 支持bank选择预充电策略

框图

从框图可以看出,控制器包括总线接口部分,调度程序部分,内存接口部分。

CPU如果写DRAM,会将写的地址和数据放入到AXI总线上。DRAM控制器接收到该AXI数据,通过内部的电路,将数据转化为DRAM的接口时序数据,通过PHY接口,将数据写入到外部的DRAM中。

CPU如果读DRAM,会将读的地址放入到AXI总线上。DRAM控制器接收到该AXI数据,通过内部的电路,将数据转化为DRAM的接口时序数据,通过PHY接口,将外部的DRAM数据读取到内部的read date fifo中,然后发送回CPU。

2. DRAM初始化

初始化包括:

l PHY DLL 初始化:设置PHY的DLL。

l 设置控制寄存器:设置DRAM控制器的参数,使DRAM控制器的参数与外部DRAM芯片的参数一致。

l 内存初始化:对外部的DRAM芯片进行初始化。对于内存初始化,参考JEDEC标准和存储设备的数据手册。有三种不同的存储设备,LPDDR,LPDDR2,DDR2。

3. AXI地址映射

地址映射:

控制器会映射AXI的地址信息映射到DRAM设备的地址,如片选,bank地址,row地址,col地址。这样,CPU就可以通过AXI直接对外部DRAM设备进行数据访问。

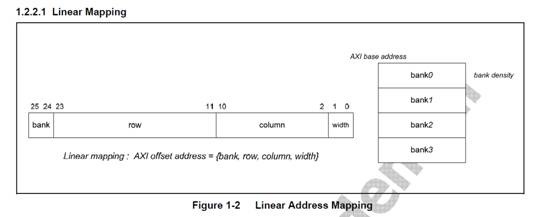

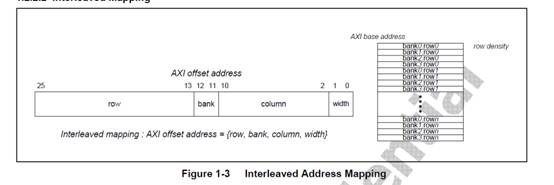

AXI的地址被分为AXI base地址和AXI offset地址。

AXI base地址决定存储设备的开始地址,AXI offset决定存储设备基于开始地址的偏移地址。而AXI的地址,由bank,row,col来组合而成。因为该组合不是唯一的,因此就存在多种映射关系。该映射关系由memconfig寄存器设置。

映射有两种,不过一般是使用线性映射:

1、 线性映射

2、 交错映射

s5pv210给出了外接DRAM的解决方案:

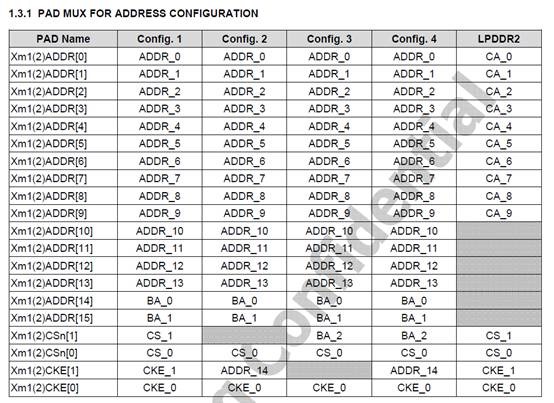

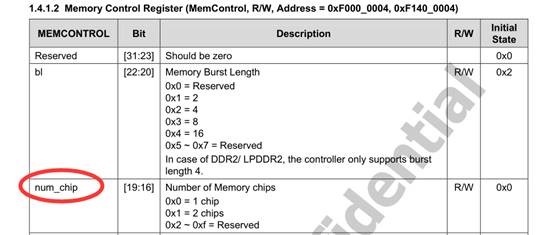

也有说明

l config.1:不大于4bank,并且row的地址不大于14bit

l config.2:不大于4bank,并且row的地址不大于15bit

l config.3:8bank,并且row的地址不大于14bit

l config.4:8bank,并且row的地址不大于15bit

l config.5:memory的类型是LPDDR2

对于不同的DRAM的bank和row地址,使用不用的解决方案。对于x210-v3开发板,使用的是8bank,14位的row地址,所以使用的是config.3方案。和原理图设计的一样。

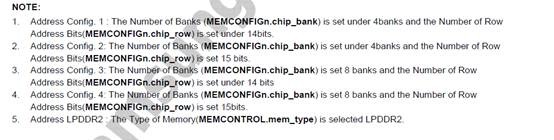

当DRAM是8bank,CS1管脚复用为bank2,这个时候210相当于只有一个片选CS0。这样,DRAM控制器就只能控制一个chip了,通过CS0来控制,这个时候就要设置memcontrol寄存器的num_chip为0,表示外接的存储器是一片。这样,就不需要配置memconfig1寄存器了,因为用不到第二个片选CS1。

memconfigx(x=0,1)是chipx的配置寄存器。每个DMC都有该寄存器。而且是两个,表示针对片选0和片选1。

对于地址映射:

210可以控制内存地址映射,DMC0的地址空间是0x2000_0000 – 0x3fff_ffff。DMC1的地址空间为0x4000_0000 – 0x7fff_ffff。DMC可以通过配置寄存器Memconfig寄存器来使内存芯片映射到内存段内的适当位置。

如果设置chip_base为0x20。也就表示为DRAM的起始地址是0x2000_0000。

1. 挂载的内存为128M,chip_mask应该设置为0xf8。表示DRAM的地址为0x2000_000-0x27ff_ffff,该chip选中。

2. 挂载的内存为256M,chip_mask应该设置为0xf0。表示DRAM的地址为0x2000_000-0x2fff_ffff,该chip选中。

3. 挂载的内存为512M,chip_mask应该设置为0xe0。表示DRAM的地址为0x2000_000-0x3fff_ffff,该chip选中。

以DMC0为例,当DMC0接收到来自AXI的0x2000_0000 – 0x3fff_ffff内的地址时,会做如下处理:

1. 将AXI的高8位地址和chip_mask相与得到结果,记为X

2. 将X分别于memconfig0和memconfig1的chip_base相比较,如果相等,则打开对应的片选。

假如挂载的内存大小是128M,且CS0和CS1分别挂了一片,那么128M = 128 * 1024 *1024, 则128M内存的地址范围是0x0000_0000 – 0x07ff_ffff。高位剩余5位。那么,把memconfig0的chip_base设置为0x20,chip_mask设置为0xf8。可以保证AXI的地址是0x2000_0000 – 0x27ff_ffff,这些地址与chip_mask后与,结果是0x20,与memconfig0的chip_base一致,说明访问chip0,于是chip0的片选就会有有效。

为了保持内存连续,需要将memconfig1的chip_base设置为0x28,chip_mask设置为0xf8。

这样,当AXI的地址发来是0x23xx_xxxx, 0x23 & 0xf8 = 0x20, 和memconfig0的chip_base一样,而0x23 & 0xf8 = 0x20,和memconfig1的chip_base不一样,所以会打开片选0。当AXI的地址发来是0x28xx_xxxx,0x28 & 0xf8 = 0xf8,与memconfig1的chip_base一样,与memconfig0的chip_base不一样,所以会打开片选1。而此时,地址空间就连续了起来。

当使用的DRAM是8bank时,CS1会被复用成bank2。所以这个时候只有一个chip信号CS0有效,就不需要配置CS1的寄存器memconfig1。不过要将memcontrol寄存器的num_chip为0,表示外接的存储器是一片。