systemverilog的参数化类

0赞

发表于 2017/3/19 下午10:43:59

阅读(9288)

sv中提供了参数化类,该类的参数,在定义的时候,没有固定,而是在调用的时候,确定的。参数化类,类似于C++的模板。

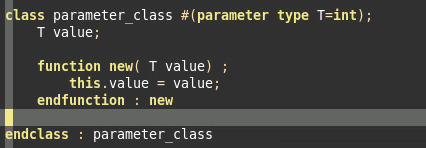

定义的格式:

class class_name #(parameter type T=类型);

如以下:

如果传参,T为int,那么内部所有的T都是int。

如果传参,T为string,那么内部的所有的T都是string。

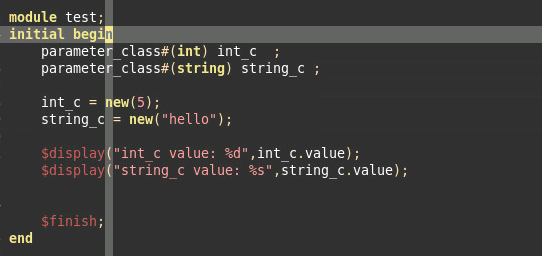

测试代码:

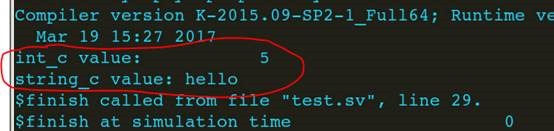

执行结果:

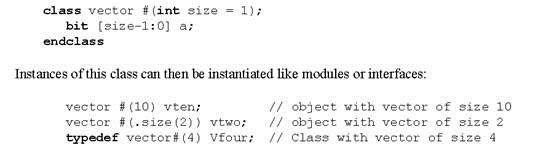

如果参数,不是类型,而是值传递,如以下:

外部传递不同的size的值,改变类中的变量a的位宽。