system verilog变量定义编译失败

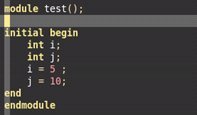

0赞sv中,变量定义,要放在程序的最开头。比如如下:

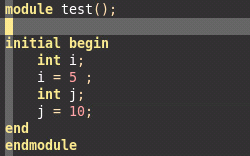

这样,编译才能成功。但是如果,变量定义没有放在最前面,而是放到了赋值语句之后,就会编译报错:

VCS编译,就会出现如下错误:

Error-[SE] Syntax error Following verilog source has syntax error : "test.sv", 7: token is 'int' int j; system verilog keyword 'int' is not expected to be used in this context. 1 error |

irun编译,就会出现如下错误:

file: test.sv int j; ncvlog: *E,BADDCL (test.sv,7|3): identify declaration while expecting a statement. module worklib.test:sv error: 1, warning: 0 |

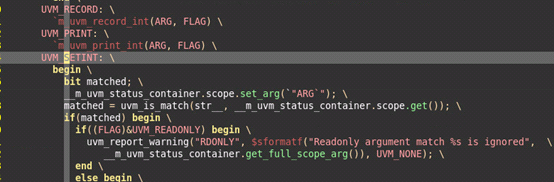

但是在看UVM源代码的时候,发现UVM中,定义一些宏的时候,会定义一些变量,那么宏在使用的时候,就会在代码的中间定义变量,也就是定义的变量没有定义在程序的最开始,但是,编译却不会报错,这又是为什么了?

如以上代码,定义了matched的局部变量。但是这个代码编译,是不会报错的。

通过测试,发现了如下的规律:

- 在1个代码块中,变量必须要定义在最前面。

- 代码块如果有嵌套,那么变量定义遵循自己所在的代码块的变量定义要求。

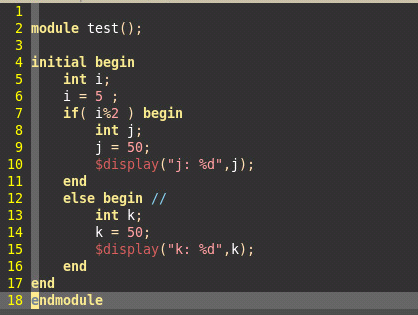

直接上代码:

如上代码,有3个代码块:

- 1是initial begin end包含的代码

- 2是if begin end包含的代码

- 3是else begin end包含的代码

每个代码块中,可以定义变量,但变量的定义,要在本代码块的最开始。否则就会出现编译失败。

变量i定义在1代码块的开始,编译不会失败,变量j是定义在2代码块的开始,因此编译不会失败。变量k是定义在3代码块的开始,因此编译也不会失败。