VCS与verdi联合进行单步调试

0赞我们在验证的时候,会有对自己写的验证代码进行debug的时候,往往在这个时候,我们基本是通过$display,系统函数来打印我们关心的东西,然后进行debug。但是这样的效率是很低的。

vcs提供了单步调试的功能,并且能够配合verdi工具。利用这两个工具,可以方便我们进行debug。

如以下的UVM验证环境:

- flist: file list,包含了环境中需要编译,仿真的文件

- get_file.sh: 自动生成flist文件的脚本

- Makefile: 执行编译,仿真的makefile

- source: RTL 源代码目录

- top_tb.sv: 验证环境顶层

- uvm_code: UVM验证代码目录

在VCS编译的时候,要额外加上 -debug_access+all -kdb -lca 这个三个选项参数。这样,之后生成的simv,才能支持单步调试功能。

即 vcs -debug_access+all -kdb -lca

makefile的vcs目标,对代码进行编译,生成simv。

生成simv后,要增加一个选项,-gui=verdi,表示使用verdi这个工具进行单步调试。

makefile的sim目标,代码仿真,进行单步调试。

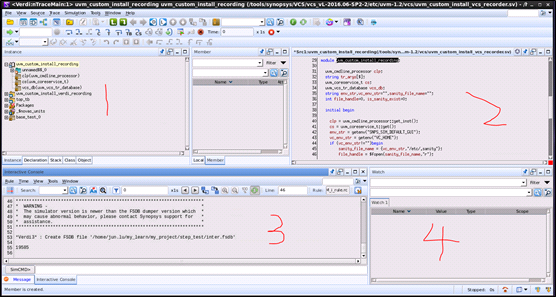

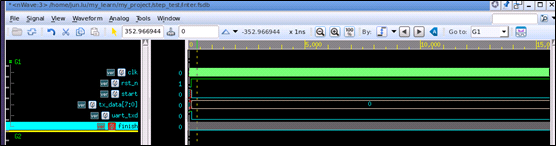

执行 make vcs; make run 后,会弹出verdi界面,并且停在0时刻。

此时界面,如下所示,1处为代码结构,2为代码区,3为交互式窗口,4为watch窗口。

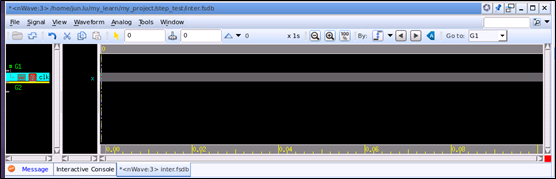

此时打开波形,时刻停在0时刻,信号还没有产生波形。

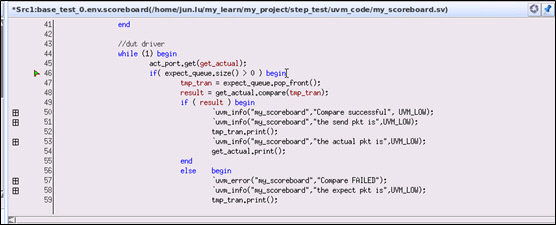

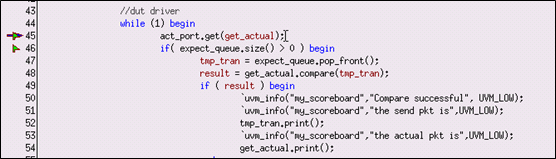

在scoreboard中,设置断点,查看接收的包信息。

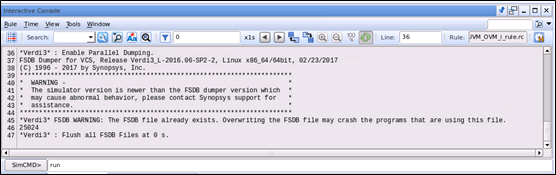

在交互式窗口,输入run,或者快捷键F5,或者菜单栏Simulation->Run/Continue。运行仿真。

此时,仿真会在断点处停下来。

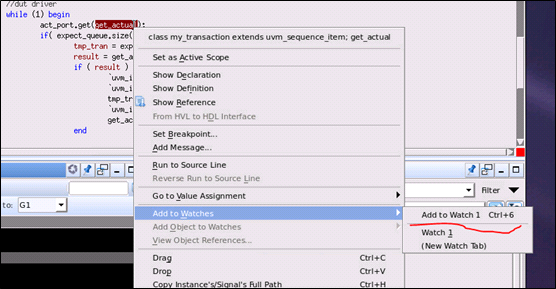

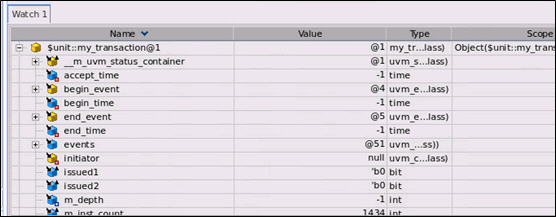

对get_actual变量,右键,Add to Watches->Add to Watch 1。将变量添加到watch中。

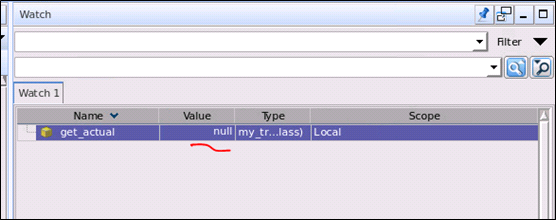

因为,此时这个变量,还没有获取到值,因此值为null。

在交互式窗口输入next,或者快捷键F10,或者菜单栏 Simulation->Step/Next->Next。

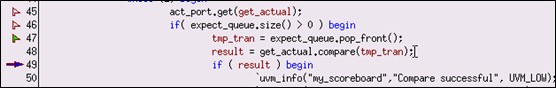

执行到获取包。将包添加到watch中。

此时,包就不是null,而是有值了,可以查看包中各个变量的值。

此时,波形也会显示到当前仿真时刻,各个信号的波形。

通过这种,方式,是不是debug,就容易很多了。