ARM GIC(二)中断术语

0赞

发表于 2018/7/12 下午9:57:19

阅读(4741)

ARM在GIC中,对于中断,定义了如下的一些术语。

一、中断状态

对于每一个中断而言,有以下4个状态:

- inactive:中断处于无效状态

- pending:中断处于有效状态,但是cpu没有响应该中断

- active:cpu在响应该中断

- active and pending:cpu在响应该中断,但是该中断源又发送中断过来

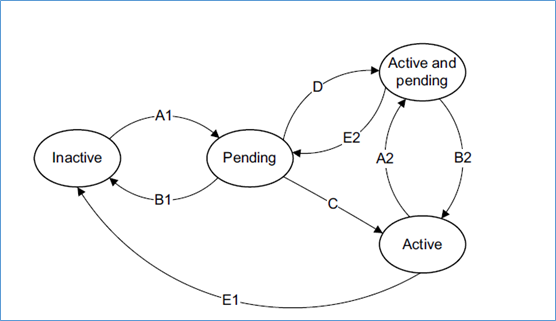

以下是中断状态的转移图。至于图中的转移条件,在gic架构文档中,有介绍。

二、中断触发方式

中断触发方式,包含以下两种方式:

- edge-triggered: 边沿触发,当中断源产生一个边沿,中断有效

- level-sensitive:电平触发,当中断源为指定电平,中断有效

三、中断类型

中断类型分为以下几类:

- PPI:(private peripheral interrupt),私有外设中断,该中断来源于外设,但是该中断只对指定的core有效。

- SPI:(shared peripheral interrupt),共享外设中断,该中断来源于外设,但是该中断可以对所有的core有效。

- SGI:(software-generated interrupt),软中断,软件产生的中断,用于给其他的core发送中断信号

- virtual interrupt:虚拟中断,用于支持虚拟机

四、中断优先级

因为soc中,中断有很多,为了方便对中断的管理,对每个中断,附加了中断优先级。在中断仲裁时,高优先级的中断,会优于低优先级的中断,发送给cpu处理。

当cpu在响应低优先级中断时,如果此时来了高优先级中断,那么高优先级中断会抢占低优先级中断,而被处理器响应。

五、中断号

为了方便对中断的管理,gic为每个中断,分配了一个中断号,也就是interrupt ID。对于中断号,gic也进行了分配:

- ID0-ID15,分配给SGI

- ID16-ID31,分配给PPI

- ID32-ID1019分配给SPI

- 其他

在具体的arm的cpu中,对于PPI,又进行了详细的分配。这个,就得看arm cpu的TRM了。

六、中断生命周期

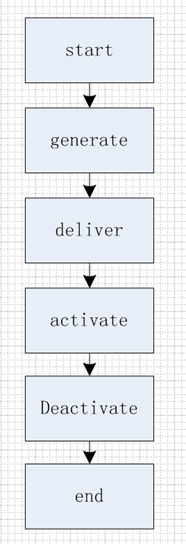

一个中断,是有生命周期的。以下是流程图:

- start:中断开始

- generate:中断源产生中断,发送给gic

- deliver:gic将中断发送给cpu

- activate:cpu响应该中断

- deactivate: cpu响应完中断,告诉gic,中断处理完毕,gic更新该中断状态

- end:中断结束

七、banking

banking(不知翻译成啥比较合适)功能,包括以下两个:

1、中断banking

对于PPI和SGI,gic可以有多个中断对应于同一个中断号。比如在soc中,有多个外设的中断,共享同一个中断号。

2、寄存器banking

对于同一个gic寄存器地址,在不同的情况下,访问的是不同的寄存器。例如在secure和non-secure状态下,访问同一个gic寄存器,其实是访问的不同的gic的寄存器。

具体,更多的信息,得看gic spec以及arm spec。

更多内容,请看我的个人网站:http://www.lujun.org.cn/