ARM GIC(七)gicv3架构-power控制

0赞从gic3开始,cpu interface放到了PE中,因此cpu interface和PE是同一个power domain。而属于gic的其他组件,如redistributor,distributor,是另外一个power domain。因此就有如下一种情况,PE和cpu interface的电源给断掉了,而gic的电源并没有断掉。此时gic给cpu interface发送数据,cpu interface是不会响应的。

在这种情况下,gic提供了power管理功能。

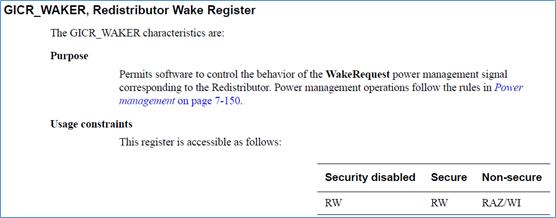

一、GICR_WAKER寄存器

gic中,提供了如下的 GICR_WAKER 寄存器,来支持power功能。

其寄存器描述如下:

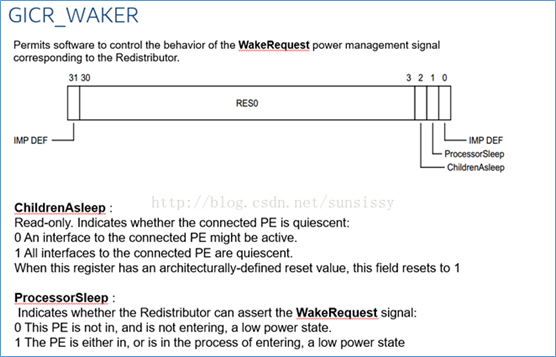

二、断电cpu interface和PE

在cpu interface和PE要断电之前,软件要保证,通知redistributor,cpu interface和PE要进入low-power状态。软件,要往GICR_WAKER寄存器的ProcessorSleep字段,写入1,表示PE要进入到low-power状态。cpu interface之后将自己置为low-power状态之后,就将ChildrenAseep字段,设置为1。

当GICR_WAKER.ChildrenAsleep为1之后,redistributor,不会在将中断,发送给cpu interface,distributor,在中断仲裁时,也不会考虑该PE。

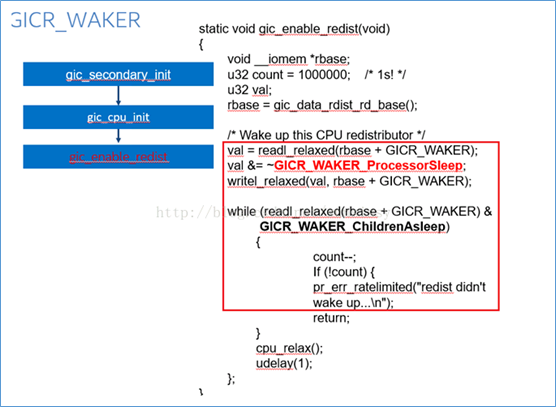

三、唤醒cpu interface和PE

当gic要唤醒cpu interface和PE时,也是操作这个 GICR_WAKER寄存器。

将processorsleep,写入0,然后去唤醒该cpu,最后读取childrenasleep,判断PE是否唤醒成功,