VIVADIO 2017.4 QSPI FLASH 下载说明

0赞VIVADIO 2017.4 QSPI FLASH 下载说明

Xilinx VIVADIO 软件版本更新到2017以后,QSPI FLASH 下载总是遇到各种奇葩的问题,用了好长时间,也没有找到好的办法解决,最近官方终于给出了解决办法。当然这个办法说的也并不是很清楚,需要自己猜和测试,一直对X的软件无力吐槽。现在这个问题终于暂时解决了,下面向大家分享QSPI FLASH下载解决方法,如有不同意见欢迎批评指正。

1、QSPI FLASH 下载,官方说明。

XILINX官网中Xilinx Answer 70548和Xilinx Answer 70148提供了VIVADIO 2017.3版本QSPI FLASH下载方法。

Xilinx Answer 70548内容如下:

翻译成中文:

描述 QSPI编程要求器件以JTAG模式启动,如program_flash输出日志所述。 初始化完成,编程内存 BOOT_MODE REG = 0x00000001 警告:[Xicom 50-100]当前启动模式为QSPI。 虽然强烈建议使用JTAG启动模式,但是在QSPI启动模式下启动设备有一种解决方法。 |

翻译成中文:

处理方法 从2017.3开始,为Zynq-7000编程闪存需要您指定FSBL。 见 (Xilinx Answer 70148). 这个FSBL用于初始化系统(主要是运行ps7_init()函数)。 如果在QSPI引导模式下启动,则此FSBL将尝试从flash加载分区,从而导致flash编程的错误行为。 通过以下修改,我们将此FSBL(仅用于flash编程)限制为基本上仅运行初始化(ps7_init())。 创建一个新的FSBL项目并添加以下更改(main.c)以将其用于SDK中的Flash编程。 /* * Read bootmode register */ BootModeRegister = Xil_In32(BOOT_MODE_REG); BootModeRegister &= BOOT_MODES_MASK; //add this line to trick boot mode to JTAG BootModeRegister = JTAG_MODE; 这可以防止FSBL在编程运行时从Flash设备加载任何现有分区。 |

Xilinx Answer 70148内容如下:

翻译成中文:

描述 从2017.3版本开始,Vivado硬件管理器和XSDK要求您指定FSBL以编程QSPI闪存。 这样做是为了在Zynq-7000和Zynq UltraScale +之间实现共同流程。 |

翻译成中文:

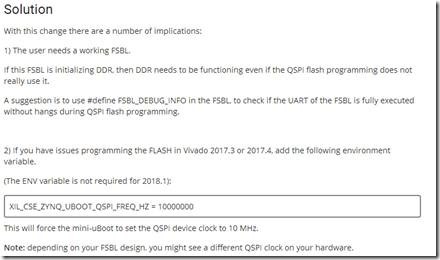

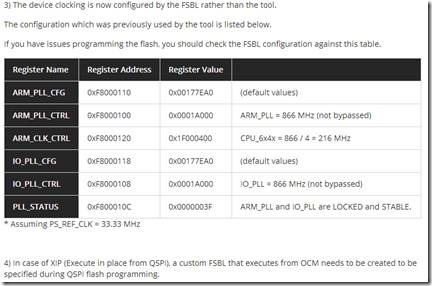

随着这种变化,带来很多影响 1) 用户需要一个有效的FSBL 如果这个FSBL正在初始化DDR,那么即使QSPI闪存编程没有真正使用它,DDR也需要运行。 建议在FSBL中使用#define FSBL_DEBUG_INFO,以检查在QSPI闪存编程期间FSBL的UART是否完全执行而没有挂起。 2) 如果您在Vivado 2017.3或2017.4中编程FLASH时遇到问题,请添加以下环境变量。 (2018.1不需要ENV变量): XIL_CSE_ZYNQ_UBOOT_QSPI_FREQ_HZ = 10000000 这将强制mini-uBoot将QSPI器件时钟设置为10 MHz。 注意:根据您的FSBL设计,您可能会在硬件上看到不同的QSPI时钟。 3) 设备时钟现在由FSBL而不是工具配置。 下面列出了该工具以前使用的配置。 如果您在编程闪存时遇到问题,则应根据此表检查FSBL配置。 4) 对于XIP(从QSPI执行),需要在QSPI闪存编程期间,指定从OCM执行的自定义FSBL。 |

2、QSPI FLASH 下载,分析说明。

从官方的文档中,经过分析和实际操作,总结以下信息。

(1)“指定fsbl”文件修改

根据文档说明,从VIVADO 2017.3版本开始,Xilinx官方为了使Zynq-7000和Zynq UltraScale +实现流程相同,在QSPI FLASH使用上做了变化,即Zynq-7000编程flash需要“指定的fsbl”。这个fsbl用于初始化系统(主要是运行ps7_init()函数)。

通过分析可知下载QSPI FLASH 的“指定的fsbl”文件与生成boot.bin文件的fsbl文件不同,这里不能混淆。

QSPI编程要求器件以JTAG模式启动。(因为在QSPI引导模式下启动,则“指定的fsbl”将尝试从flash加载分区,从而导致flash编程的错误行为。导致不能下载flash或下载flash后不能启动。)官方给出了修改方法,通过在“指定的fsbl”中的main.c中如下位置添加如下语句,防止FSBL在编程运行时从Flash设备加载任何现有分区。

/*

* Read bootmode register

*/

BootModeRegister = Xil_In32(BOOT_MODE_REG);

BootModeRegister &= BOOT_MODES_MASK;

//add this line to trick boot mode to JTAG 添加的语句

BootModeRegister = JTAG_MODE;

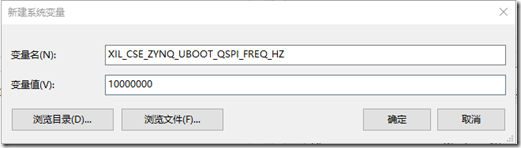

(2)环境变量修改

VIVADO 2018.1不要设置环境变量。

VIVADO 2017.3,VIVADO 2017.4版本下载QSPI FLASH需要设置环境变量。

变量名:XIL_CSE_ZYNQ_UBOOT_QSPI_FREQ_HZ

变量值:10000000

这么做的目的是这将强制mini-uBoot将QSPI器件时钟设置为10 MHz(根据您的FSBL设计,您可能会在硬件上看到不同的QSPI时钟)。

3、QSPI FLASH下载,操作说明。

软件版本:VIVADO 2017.4

开发板:MIZ7035(xc7z035-ffg676)

(1) 新建环境变量

计算机à属性à高级系统设置à高级à环境变量à新建系统变量

变量名:XIL_CSE_ZYNQ_UBOOT_QSPI_FREQ_HZ

变量值:10000000

(2) 生成BOOT.BIN文件

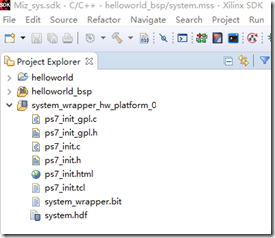

加载到SDK

新建fsbl工程,FileàNewàApplication Project,输入fsbl,点击Next。

选择Zynq FSBL,点击Finish

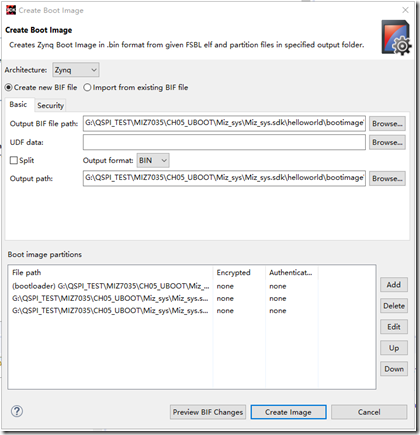

选中工程(helloworld),右击,选择Create Boot Image。

Boot image partitions包含三个文件,分别是fsbl.elf、system_wrapper.bit、helloeorld.elf。

Output BIF file path是bif数据文件路径。Output path是BOOT.bin的输出路径。

单击Create Boot Image。

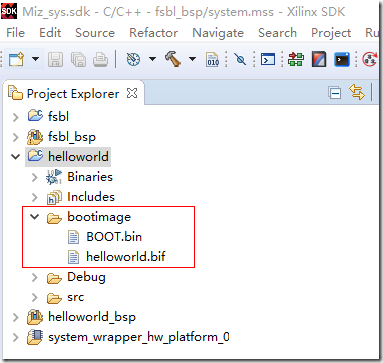

在工程(helloworld)中生成bootimage文件。单击打开bootimage,生成的BOOT.bin文件。

(3) 生成加载QSPI FLASH的fsbl文件

新建一个新的FSBL文件,命名为fsbl_load。FileàNewàApplication Project,输入fsbl_load,点击Next。

打开fsbl_load的main.c文件,在此处增加“BootModeRegister = JTAG_MODE; ”保存并编译。

(4) 下载

模式开关切换到QSPI启动模式(1-ON ,2-OFF)。

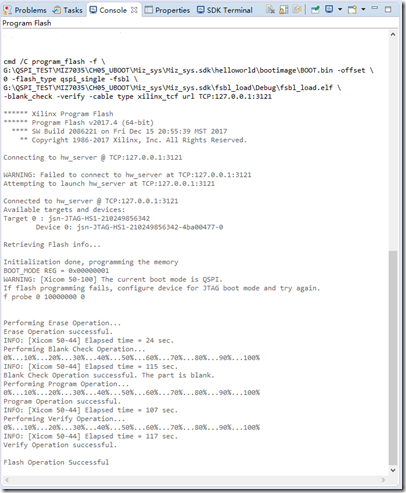

单击 Program Flash Memory

加载刚才生成的BOOT.BIN文件和fsbl_load文件,单击Program。

下载

Console打印

断电,重新打开电源,开发板加载QSPI flash。

4、总结

Xilinx 的软件无力吐槽,不断变换花样,只能根据实际情况做相应的处理。大家不断努力攻克问题,共同学习。

转载说明:转载请标明文章来源于常州一二三/米联电子 。

参考链接:

1、 https://www.xilinx.com/support/answers/70548.html (Xilinx Answer 70548)

2、 https://www.xilinx.com/support/answers/70148.html(Xilinx Answer 70148)