FPGA模块划分

0赞模块划分基本原则:

(1)对每个同步时序设计的子模块的输出使用寄存器(用寄存器分割同步时序模块原则)。

(2)将相关逻辑和可以复用的逻辑划分在同一模块内(呼应系统原则)。

(3)将不同优化目标的逻辑分开。

(4)将送约束的逻辑归到同一模块。

(5)将存储逻辑独立划分成模块。

(6)合适的模块规模。

(7)顶层模块最好不进行逻辑设计

块划分和复用:

1、时钟生成模块单独填加到TOP模块

时钟生成模块单独填加到TOP模块,来驱动其他子模块A、B、C等。

2、根据时钟域对模块划分

不同时钟域划分到不同的模块中,中间用同步逻辑隔开。

3、使用寄存器分割同步时序模块

建议对每个同步时序逻辑的输出使用寄存器,这样能使得输出信号的强度和延时都可以欲知,并保证输入到第二级时的延时相同。

4、将相关的组合逻辑划分到同一个模块中

同一类型能合并在一起的组合逻辑就合并在一起,尽量使一个FF,一个组合逻辑块,一个FF,一个组合逻辑块。

5、可以复用的资源划分在一个模块里

可以通过一个算法,一个函数复用的分在一个模块里,可以供以后复用做准备。复用可以省面积,但耗速度。

6、根据不同优化目标划分

建议将时序关键路径逻辑划分到单独模块,设置speed;非关键路径可以设置area。

7、对松约束的逻辑划分到同一模块

8、对异步逻辑的划分

一个异步逻辑,一个同步逻辑,一个异步逻辑,一个同步逻辑

9、避免多周期路径

将多周期路径划分到同一路径上,并添加约束。

10、状态机划分到同一模块

11、RTL级和行为级分开

12、避免顶层中包含逻辑门

应该将逻辑门合并到子模块中去

进行模块化设计的方法

1.系统划分

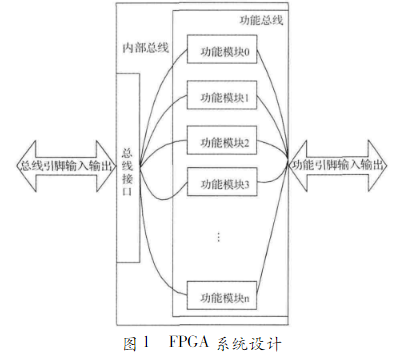

实际上,大多数的FPGA设计是基于以下模型,根据总线对寄存器的操作来完成预定功能的实现。按照功能划分的方法,把FPGA设计划分为两大部分:总线接口和功能模块,如图1所示

总线接口负责把形形色色的外部总线转化为统一的FPGA内部同步总线。同时,提供主系统对各寄存器的读写操作支持逻辑。

功能模块负责以寄存器表为中介实现各功能,在设计功能模块时把总线接口和功能接口分类排列,保障各功能模块总线接口的一致性。

2.总线接口

结合同步设计的思想和FPGA设计的基本原则,制定以下内部总线规范:

1)内部总线负责通过总线接口与主控机进行数据交互。

2)内部总线以功能模块为单位分组。3)每组信号的组成:

Rd_en:读操作使能信号,高电平有效,持续1个时钟周期;

Wr_en:写操作使能信号,高电平有效,持续1个时钟周期;

Clk:系统时钟;

Mi_regs_en:模块寄存器操作允许信号,高电平有效,持续时间不短于寄存器进行读、写操作所需周期;

Data_in:模块数据输入总线;Data_out:模块数据输出总线。关于规范的说明:

随着同步化设计思想的普及和发展,大多数总线都包含1个参考时钟,各总线信号的变化由同一时钟的同1个沿驱动。对于少数的异步总线,我们可以通过引入1个高频时钟的方法把异步总线改造为同步总线。然后分析总线对于外设的操作:在主流的以寄存器表为中介的FPGA逻辑设计中,总线对与外设的控制可以抽象为对1个或1组对寄存器的读写操作。所以内部总线只需要可以便捷的进行同步寄存器读写操作即可。而数据线在外部是作为双向总线使用的,但在FPGA内部进行设计时,很少在逻辑处理时采用双向数据总线,所以把外部数据总线改造为模块数据输入总线和模块数据输出总线两组单向数据总线。

总线接口分为3个逻辑单元:总线译码、总线多路选择和总线缓冲,如图2所示