简单的verilog串并转换 程序

0赞串并转换的简单实现方法,用计数器的最低位作为时钟sclk,用移位寄存器降数据串行输出。

`timescale 1ns/1ns

module p2s

(

input clk,

input rst_n,

input load,

input [7:0] pdata,

output sclk,

output sdat

);

`define FULL 4'hf

reg [3:0] bitcnt;

reg en;

reg [7:0] sbuff;

always @(posedge clk or negedge rst_n)

if(!rst_n) en <= 0;

else if(load) en <= 1'b1;

else if(bitcnt==`FULL) en <= 1'b0;

always @(posedge clk or negedge rst_n)

if(!rst_n) bitcnt <= 0;

else if(en) bitcnt <= bitcnt + 'b1;

else bitcnt <= 0;

assign sclk = bitcnt[0];

always @(posedge clk or negedge rst_n)

if(!rst_n) sbuff <= 8'b0;

else if(load) sbuff <= pdata;

else if(sclk) sbuff <= sbuff<<1;

assign sdat = sbuff[7];

endmodule

`timescale 1ns/1ns

module tb;

bit clk;

bit rst_n;

bit load;

bit [7:0] pdata;

wire sclk;

wire sdat;

p2s p2s

(

clk,

rst_n,

load,

pdata,

sclk,

sdat

);

initial forever #100 clk = !clk;

initial begin

#120; rst_n = 1;

repeat(16) @(posedge clk);

@(posedge clk);

#1; load = 1;

pdata = 8'ha6;

@(posedge clk);

#1; load = 0;

pdata = 8'ha6;

repeat(32) @(posedge clk);

$stop;

end

endmodule

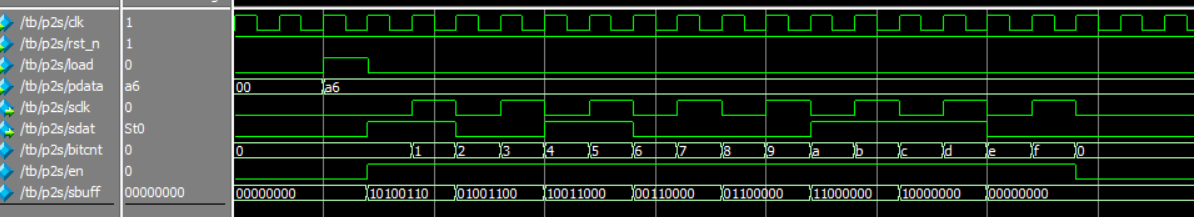

转换0xA6的仿真波形。