基于FPGA的计算器设计一(矩阵键盘模块)

1赞这周做了一个计算器的实验,目前可以正负实现数的加减乘除,以及定点小数的加减乘除,精度不高还在进一步完善,今天先把矩阵键盘扫描的模块总结一下,明天继续优化。

这是一个大概的模块划分和数据流向图,我们首先要通过矩阵键盘扫描来确定按下的键,然后把键值送给输入输出控制模块,来判断输入的是第一个操作数还是操作符,还是第二个操作数以及等号,可以说输入输出控制模块是整个计算器设计最核心的模块了,这个明天再总结,如果判断按下等号,那么计算模块就应该根据操作数和操作符来运算,并把运算的结果送到输入输出控制模块。因为在输入数据的时候,数码管也是要显示数据的,所以把计算的结果传回来一起处理,而且计算的结果也可以作为下一次计算的操作数,实现连续运算。计算模块还包括BCD转二进制以及二进制转BCD模块,另外由于涉及到负数运算,所以计算过程都是补码进行运算,计算结果再由补码转回原码,数码管显示模块和常用的数码管模块不同的地方就是它具有消“0”的功能,输入的时候每输入一位数据显示一位,对于没有输入的位数是不能显示“0”的,输出计算结果的时候也是一样,对于没有数值的位,是不能显示“0”的。

下面先总结以下矩阵键盘模块,使用矩阵键盘的原因就不多说了,就是为了节约IO口。矩阵键盘扫描的原理我简单介绍一下吧:

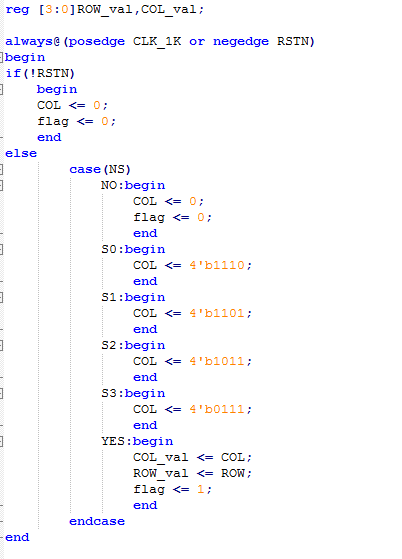

以4x4的矩阵键盘为例,同一行按键的一段被接到同一根先上,4行分别被接到4根,我们命名row0-row3;列同理,命名col0-col3。同时我们给row端接上上拉电阻,那么没有按键按下的时候row端是高电平,我们把4根row接到FPGA作为输入端,把col接到FPGA作为输出端。我们在初始状态下给col全部赋0输出,如果某一个按键按下,那么就会有一个col和一个row线被联通了,那么被联通的那根row就会给FPGA输入0,此时row是输入,我们可以很容易判断是哪根row被联通了,但是每一根row上连上了4根col,我们还不能知道具体是哪一个col,所以我们这时用到中学物理时学到的控制变量法,我们让col每次只有一根输出低电平(注意原来是4个全是低电平,在检测到有键按下后,变成只有一根输出低电平),依次扫描,知道检测到row端不全为1时,说明此时的row和col就是按下按键的坐标了。

最后例化的消抖模块是上次数字钟的消抖模块,略微做了一点修改,所以将设计模块化还是有很大帮助的。

里面的flag_pos是为了检测按键的边沿,按键按下会有一个flag标志拉高,这里检测的其实是flag的下降沿,也就是按键弹起来的时候,一开始我是检测上升沿的,但是会存在一点时序问题,因为这个flag_pos只有一个时钟周期,我如果检测上升沿输出,在flag拉高的这一刻,key_value其实还没有被赋值好,所以会导致,我按第一个按键的时候没有数据显示,按第二个的时候显示第一个按键的值,但是检测按键弹起的时刻(也就是flag的下降沿)就能有效避免这种情况。

矩阵键盘扫描的原理基本就是这样,但是实现的方法有很多种,我觉得这种方法是比较简单明了,适合新手理解的。当然我自己也还是新手,嘻嘻......加油!