《FPGA设计技巧与案例开发详解》初探(二)之工程文件管理

4赞对于彬哥书中所提到的工程文件管理,由于只给了一个框架,简要介绍了各个文件夹的作用,进而有许多初学者不知道具体怎么操作,会在群里问这类问题。下面,我将详细介绍一下如何构建彬哥的工程目录。

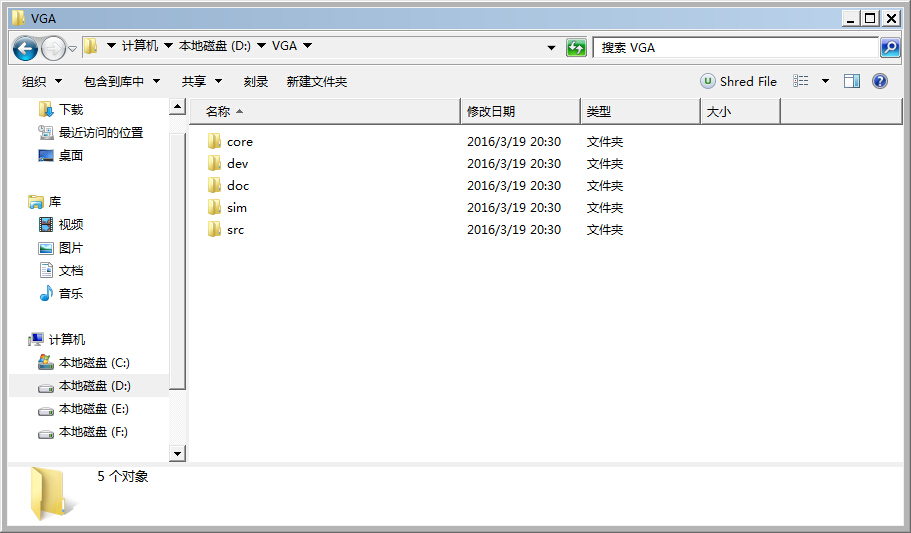

首先,我还是简要介绍一下彬哥的工程目录。其工程目录将一个FPGA工程划分为5个部分,亦即5个文件夹,如图1所示。第一个是名为core的文件夹,用于放置IP核相关的文件;第二个是名为dev的文件夹,用于放置主工程相关的文件;第三个是名为doc的文件夹,用于放置项目资料;第四个是名为sim的文件夹,用于放置modelsim仿真相关的文件;第五个是名为src的文件夹,用于放置工程子代码文件,里面还可以细化为多个子文件夹。

图1

有了上面的了解后,我们就可以构建彬哥的工程目录了,以下是具体的操作步骤:

首先,建立你的工程文件夹,如我的是在D盘的VGA文件夹,然后在里面新建上述的5个子文件夹,如图2所示。

图2

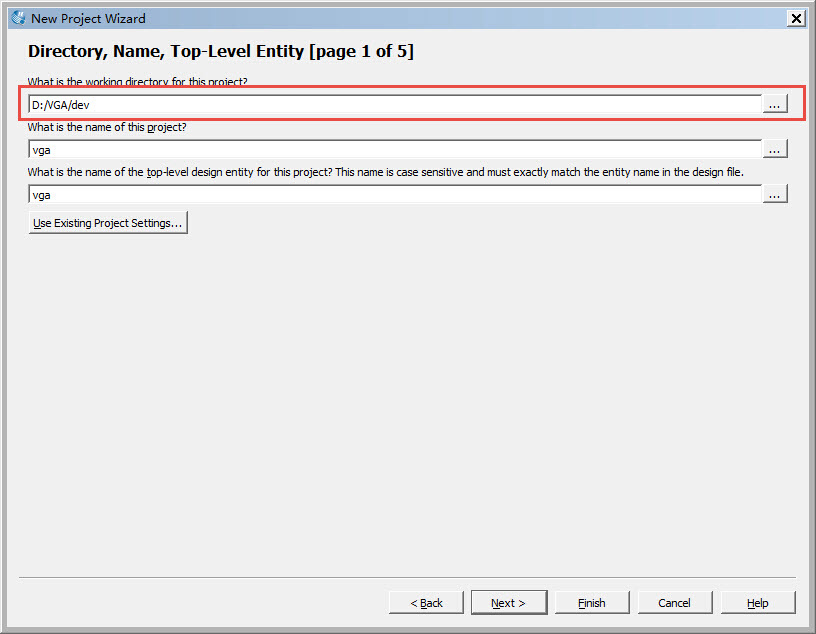

打开quartusII,建立新工程,将工程路径选取在dev文件夹里,如我的路径为D:/VGA/dev,如图3所示。然后一直Next,直到工程建立。

图3

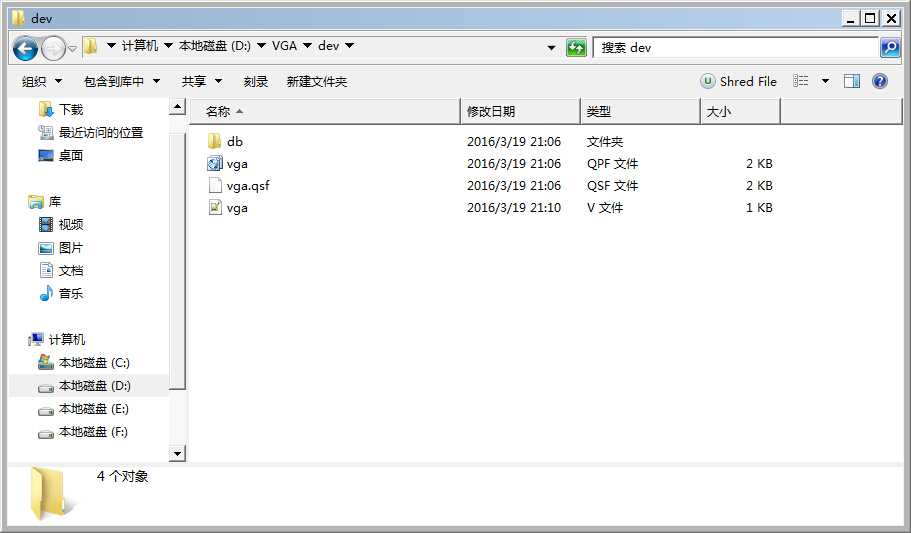

然后,新建你的verilog主文件,将其保存到dev文件夹里,进而,dev文件夹的内容如图4所示。

图4

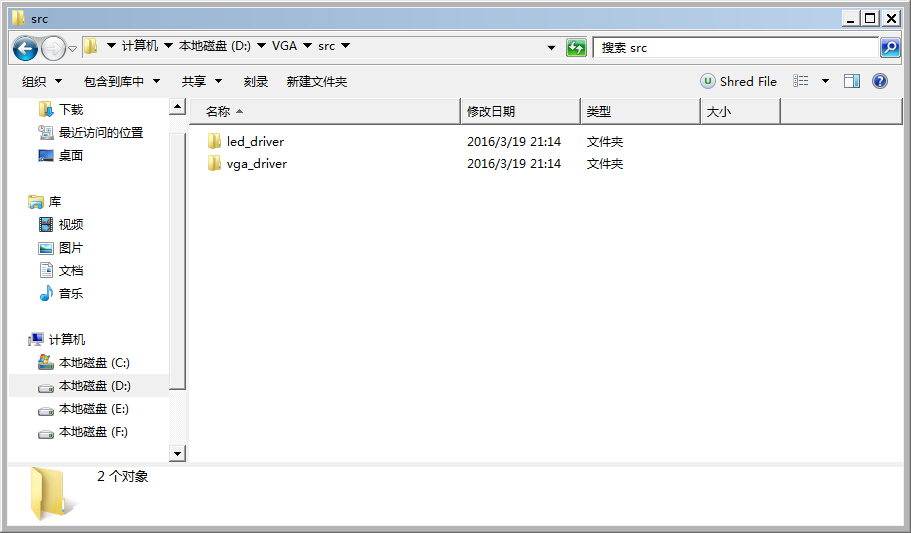

然后,新建你的多个verilog子文件,将其分类保存在src文件夹里,我这里有两个verilog子文件,一个是vga_driver.v,放在src下的lcd_driver在子文件夹里,即:D:/VGA/src/vga_driver/vga_driver.v;一个是led_driver.v,放在src下的led_driver子文件夹里即:D:/VGA/src/led_driver/led_driver.v。分别如图5,6,7所示。

图5

图6

图7

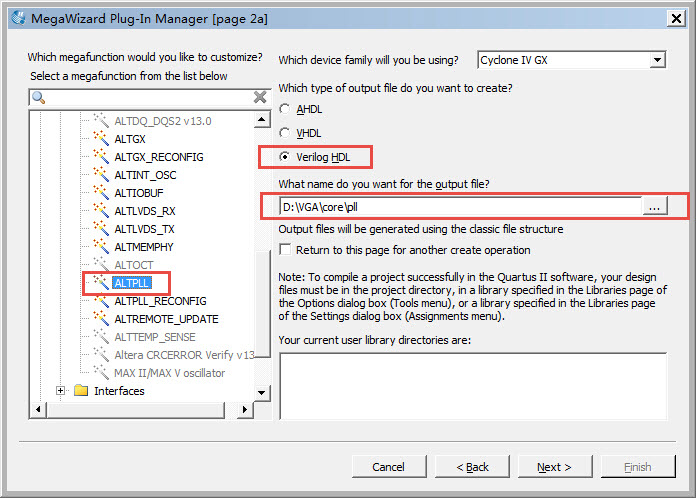

而后,如果我们需要调用IP核,就将IP核生成在core文件夹里,我这里是生成一个pll IP核,将其路径设置为D:/VGA/core/pll,如图8所示。进而,core文件夹下的内容如图9所示。

图8

图9

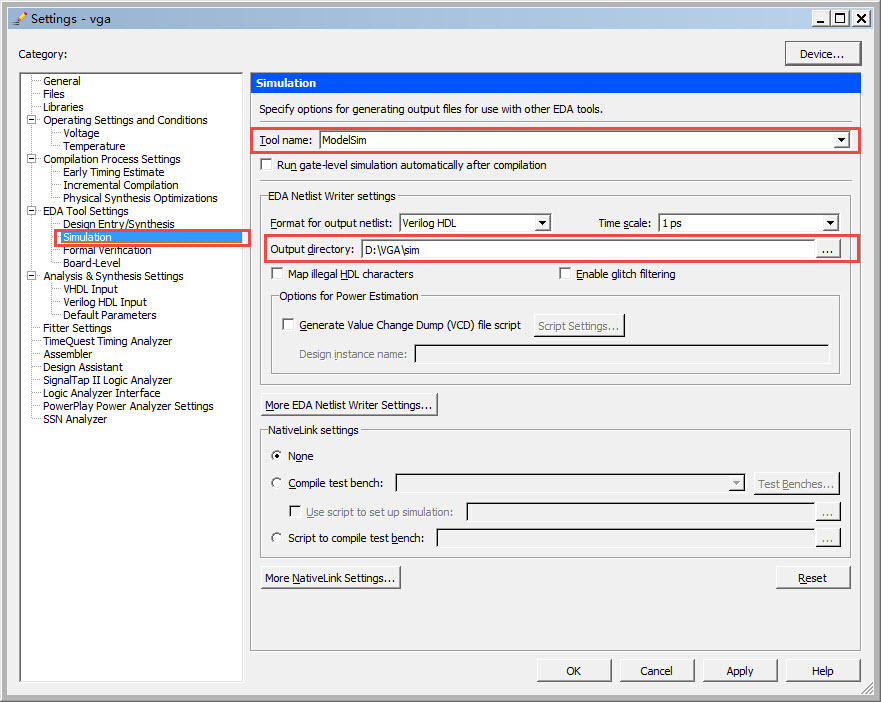

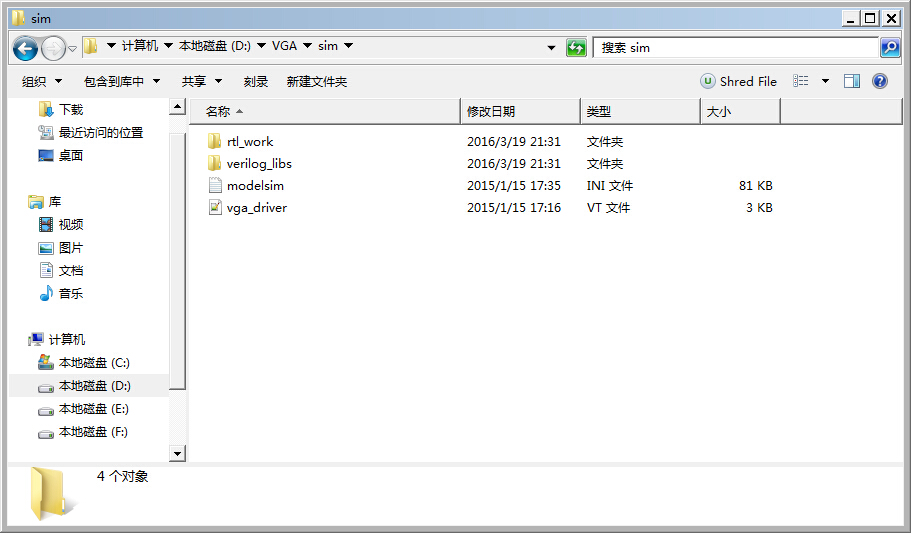

然后,如果我们需要仿真,将modelsim仿真路径设置在sim里,设置是在按钮Assignment下的Setting,点击Setting后,就如图10所示,设置modelsim仿真路径:D:/VGA/sim。并将仿真的testbench文件按照步骤4的操作保存在sim文件夹里。进而,sim文件夹下的内容如图11所示。

图10

图11

最后,如果对你的工程有些资料,心得什么的都可以放置在doc文件夹里,如我的doc文件夹里就放置了一写vga心得,如图12所示。

图12

最后,是不是感觉自己的工程很高大上,很有条理。