FPGA实现串口多比特发送接收模块

0赞一. 简介

这是FPGA之旅的第四个设计实例了,在上一例中,也就是第三例,串口通信,实现了单byte的传输。也就是每次只能传输一个btye的数据。在实际使用过程中,需要发送多byte的数据为一包数据,里面包含各种信息,例如最常见的包头和包尾。本例将在第三例的基础上,实现多byte的接收实例,以满足具体的需求。

二. 实现方法

在串口通信中数据一般为:1 bit的起始位 + 5,6,7,8bit的数据位 + 1 bit的停止位。最多一包数据为 10 bit。

其实串口协议中,并没有规定数据位为5,6,7,8,理想情况下可以为任意位。例如,两块FPGA之间通过串口通信,就可以自定义。但是呢?上位机软件支持位数只有这么几种。为了通用性,还是以上位机软件为标准。

假如说我要一次性发送5 bytes的数据 或者 一次性接收 5 bytes的数据,然后交给FPGA进行处理,那么该怎么做呢?其实也是比较容易的。只需要再设计一个模块,重复调用 5 次串口发送模块,和串口接收模块接收了 5 bytes的数据后,再进行对应的处理,就可以了。

基础的串口通信模块完成后,就只需要完成这个多bytes 的模块了。

三. Verilog 代码实现

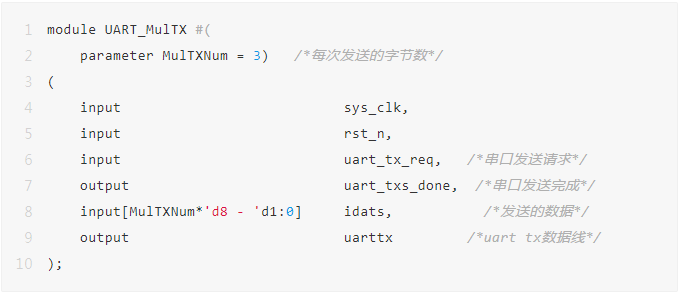

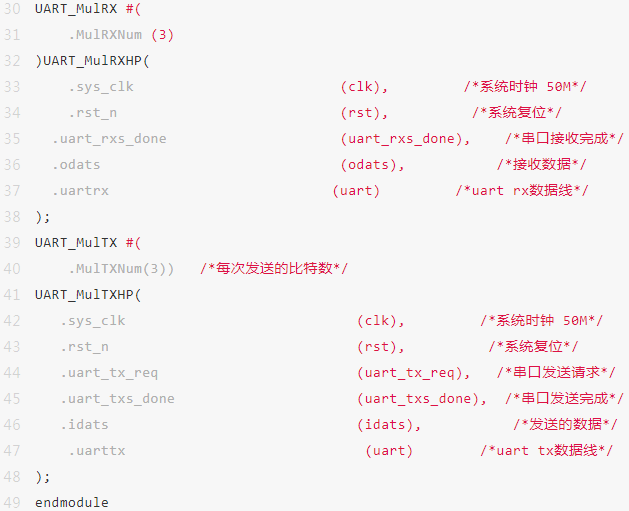

先来看一下发送的顶层模块,顶层模块,可以说和普通的串口发送模块一样,只是多出了一个参数,来控制发送字节的位宽,具体定义如下。MulTXNum通过这个参数可以在实例化这个模块的时候,自行确定每次测试字节的个数,非常灵活。

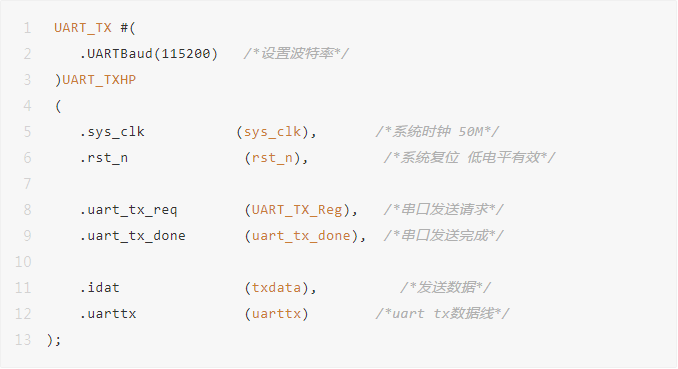

2. 在这个顶层模块中调用基本的串口发送模块。波特率也通过参数进行控制,在实例化的时候,方便修改波特率。

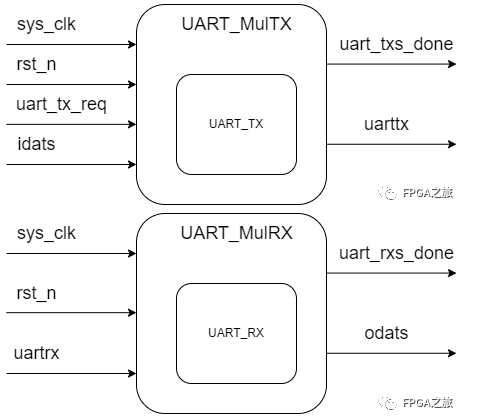

3. 串口接收模块定义也一样,具体的实现过程可以看完整的过程项目,就不粘贴上来了。需要的可以自行获取。简单看看模块图吧!

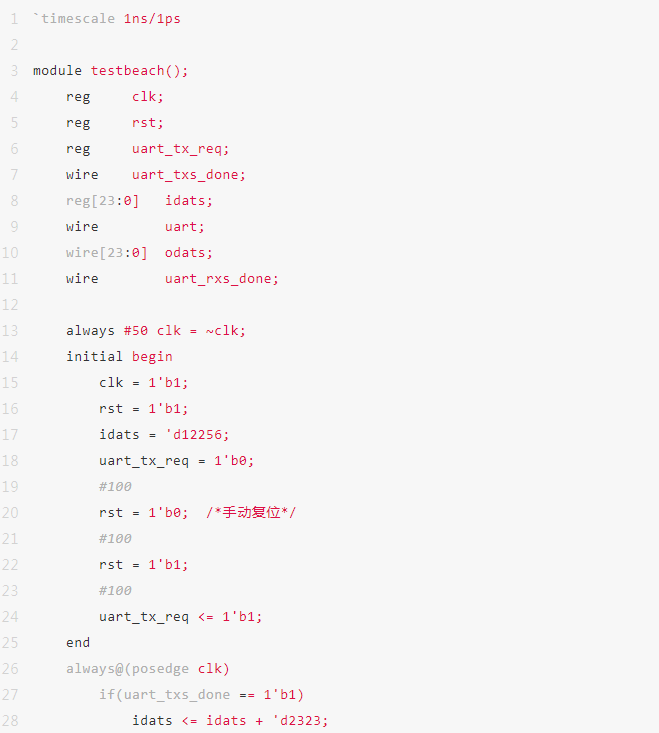

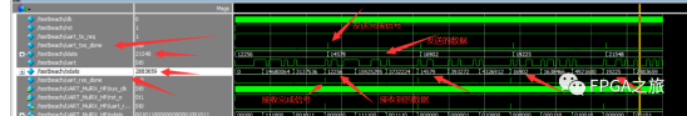

四. testbeach编写

写完各个模块后,怎么能少得了仿真呢?也是调了几次才没有bug,嗐,直接上仿真。这里测试的是每次发送3个字节的数据,每次发送完成后,发送完成后,发送数据加上2323,然后继续发送,具体的可以看看仿真波形。

通过波形可以看到,程序编写正确!!!(已上板验证)

需要完整代码的可以在公众号FPGA之旅中回复 :FPGA之旅设计99例之第四例

原文链接:https://mp.weixin.qq.com/s/-SgBkJTbW-nRkG_eqjatWQ

电子技术应用专栏作家 FPGA之旅