ALTERA的DDR2 ip核使用

0赞1、官方手册

High Performance Controllers.pdf

2、DDR2的IP核有两个,我只使用了这一个,所以就把这个先记录下来。

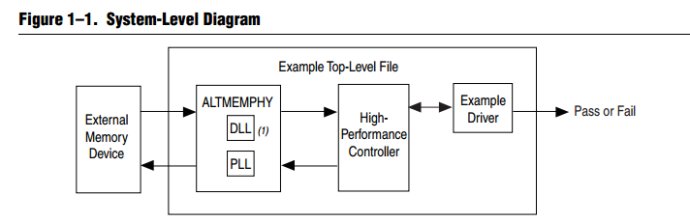

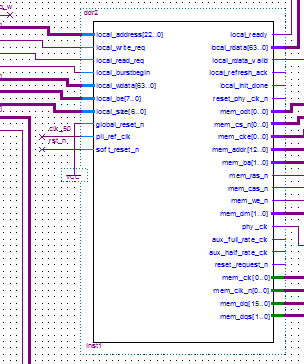

ALTMEMPHY ip核由三部分构成,一部分是最底层的SDRAM(统指动态RAM)驱动,High Performance Control对底层驱动封装了一层,具体可以打开生成IP核后的ddr2_phy.vhd(.v)看一下,之后ALTMEMPHY又在上面封装了一层,留出了用户操作DDR2的接口,该结构名称统一加了local。顶层bsf文件接口如图2:

altera之所以把一个ip核分成这么多部分(而且还是用verilog和vhdl混合编写的)而不是一个模块是因为这样做可以对这些模块实现复用,因为DDR DDR2,DDR3都采用这样的方式编写就可以复用High Perdormance Control和ALTMEMPHY,使用不同的IP核的时候只需更换底层对SDRAM的驱动即可,更加灵活和方便。

3、DDR2 ip核的时序

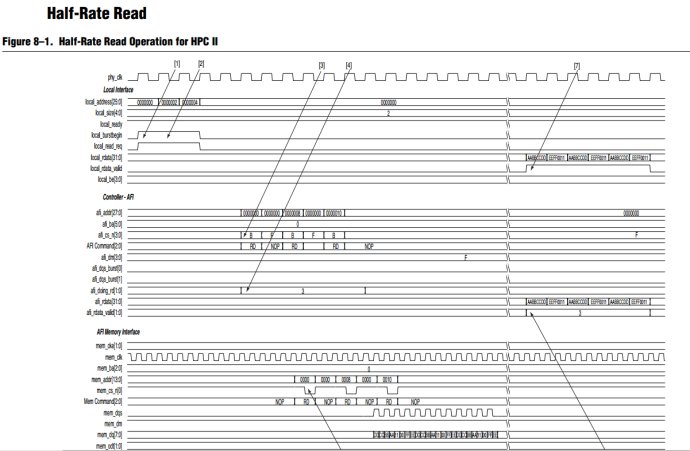

DDR2 ip核的操作时序在DDR and DDR2 SDRAM Controllers with

ALTMEMPHY IP User Guide里面,由于图比较大,仅截取其中一个时序图的部分,如图3:

该图(图3)是在半速率模式下的读时序,该图中的操作采用突发操作,突发了3次,这个IP核有一个我认为不太合适的地方就是读数据的时候读命令和数据到来之间的延时不确定,而且数据有时候不是连续来的,而是分两次或者三次(也有可能是一次)来的,所以这个给后面设计的时候增加了不少麻烦,若是读取延时时钟周期确定或者数据是连续输出的时候能省下不少麻烦。

如图3所示,在给出读命令的时候,local_burstbegin信号有效,则触发突发读操作,此时要合理设置突发的大小(local_size)和地址(local_addr)。命令发出之后,经过一段时间(一般为几个时钟周期到几十个时钟周期)之后,数据伴随local_data_valid而来。

注1:突发读操作并不需要读信号一直有效,信号有效一个周期即可被采样到。而突发写操作则需要在数据有效期间一直保持写信号有效,否则数据会丢失。

注2:半速率(half-rate)和全速率(full-rate)的区别是半速率是增加数据的位宽来降频,全速率的本地时钟(phy_clk)是半速率的2倍,数据位宽是半速率是一半。

注3:该IP核工作在High Performance Control II下可以设置命令的缓存大小(该ip核可以连续接收多个命令),若是工作在High Performance Control 下就不能改变大小,该设置可以在生成IP核的时候设置。

注4:改IP核的命令触发需要在DDR2允许接收命令的时候触发,该信号为ddr2_ready,但是在连续突发读的时候ddr2_ready有时候只有效一个周期,就立刻转为无效,此时若是采用状态机控制,在捕获ddr2_ready有效的时候就立刻转换状态发出读命令,该命令可能会被忽略,这个特点我花了两周的时间才找到,官方手册描述的还真不够细致啊。

注5:改IP核有两个复位引脚,一个是用户逻辑复位,就是那个ALTMEMPHY,另一个是全局复位(包括底层DDR2的驱动)全局复位之后DDR2芯片就要重新初始化了,如果不用全局复位的时候可以把globle_reset_n拉高,最好不要悬空。

转:http://blog.sina.com.cn/s/blog_6ac7328f0102viq4.html

参考网址

http://www.cnblogs.com/TFH-FPGA/archive/2012/08/31/2665759.html

http://blog.chinaunix.net/xmlrpc.php?r=blog/article&uid=607545&id=2088075

http://www.cnblogs.com/shengansong/archive/2012/09/01/2666213.html