SignalTap II Logic Analyzer 学习笔记

0赞

http://www.cnblogs.com/crazybingo/archive/2011/07/26/2117262.html

根据CB的博客做了一下SignalTap II,利用QUARTUS 13.0 随便写了一个小灯闪烁的verilog代码,如下:

module led

(

input clk,

input rst_n,

output led_out

);

reg [23:0]cnt = 24'd0;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 24'd0;

else

cnt <= cnt + 1'b1;

end

reg led_flag = 1'b0;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

led_flag <= 1'b0;

else if(cnt[23] == 1'b1)

led_flag <= ~led_flag;

end

assign led_out = led_flag;

endmodule

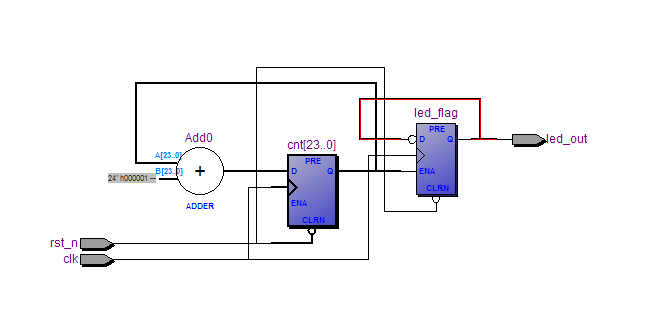

RTL如下:

照例:

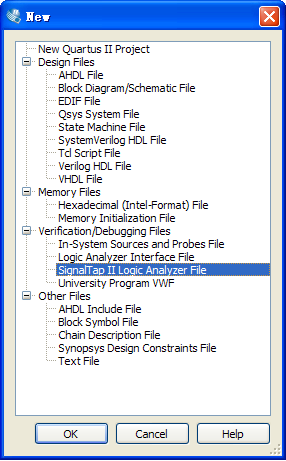

1、新建

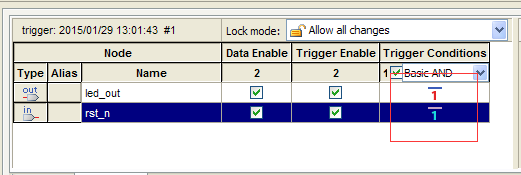

2、设置待测信号名

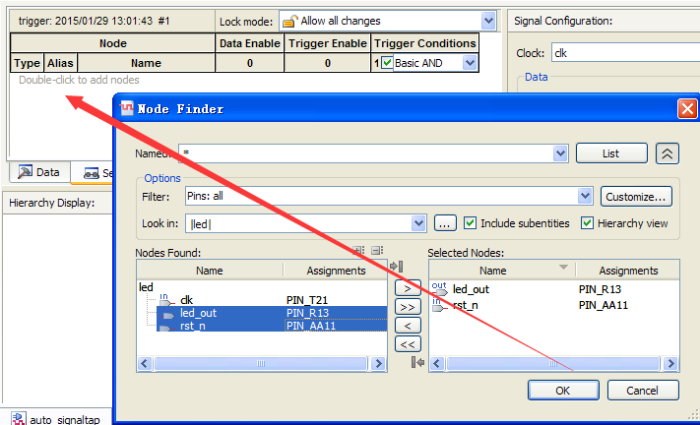

3、在node双击添加需要观察的数字信号;不要调入系统时钟,因为本例打算用系统时钟来做逻辑分析仪的采样时钟

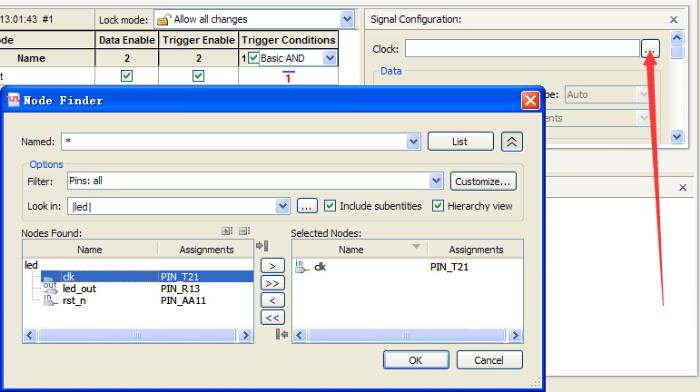

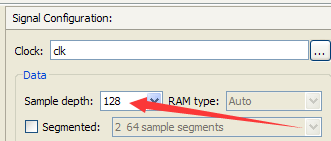

4、添加系统采样时钟(类似示波器的采样)

5、设置采样深度:因为占用ESB/M9K,采样深度最好小于9K,这里设置为2K

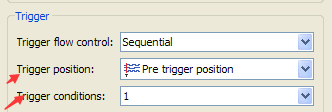

6、设置采样其实触发位置:跳变沿触发

触发方式

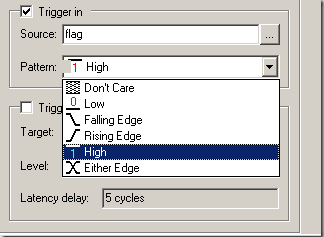

7、设置触发输入:选择触发信号以及触发方式,flag为触发使能信号,实际工程中没用,只是signaltap ii的使能信号;高电平触发,设置如下:

注意:flag为边沿采样信号,当flag变化的时候,恰好warm_data在稳态,因此将flag作为采样的触发;当然在低速地要求的情况下,flag也可以省略,SiganlTap II 会自动根据一定频率采样。

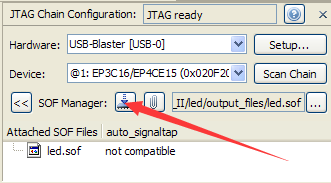

8、Save and Yes,再次编译,和本工程捆绑在一起Download to Device,(当然也可以在Settings设置);关于PIN,如果没有逻辑分析仪测试没有信号输入,如果你懒得设置,可以不分配out的信号,但是clk和rst_n必须分配,因为那是系统的驱动信号。

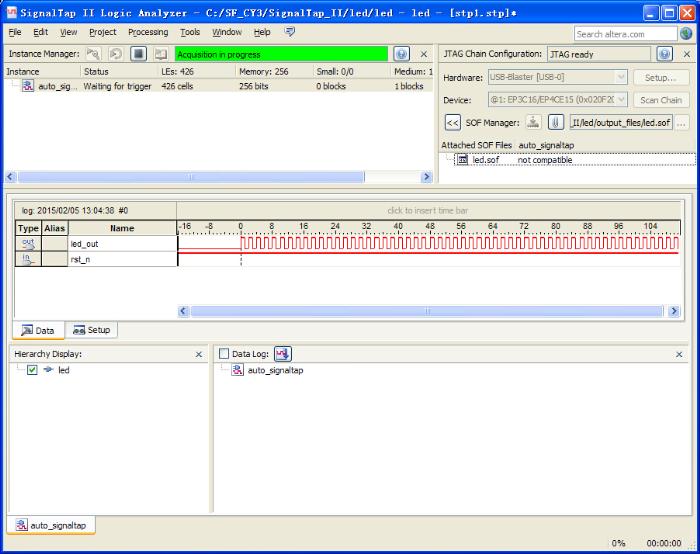

9、Download sof文件(当然也可以在Q II直接download)

10、进程—Anturon Analysis,自动分析

ok,成功验证牛人博客。可能软件版本不一样,要在

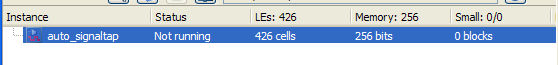

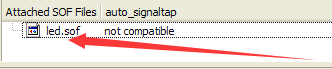

Attached SOF Files|ato_signaltap

xx.sof

右键添加.sof文件才可以看到结果

我是Quartus II 13.0

这也是我要记录这篇博客的原因。