让没有晶振的生活成为可能——UFM

0赞

五、Parallel 并行接口访问UFM ,并实现Water_LED.. 6

2. 在MegaWizard Plug-In Manager添加FLASH模块... 6

2.IP核Flash与 Oscillator共用... 12

一、 简介

传闻说CPLD有个缺陷,就是内部没有存储模块,所以不能对RAM,ROM等操作,但其实,CPLD内部有8192bits的UFM—Usr Flash Memory,很容易就可以实现RAM、ROM 的功能,能满足一时的需要。

如上图所示,MAX II 芯片Chip Planner:

左下角这块黑色区域是用户不可用资源区,而在这片不可用区域里有一块绿色的方块是可用的。这块不可用的黑色区域叫做CFM block(配置Flash存储区),而那个绿色方块叫做UFM(用户可用的Flash存储区)。

二、 特性(官方描述)

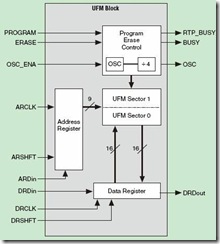

Each UFM array is organized as two separate sectors with 4,096 bits per sector. Each

sector can be erased independently

MAX II devices feature a single UFM block, which can be used like a serial EEPROM for s

toring non-volatile information up to 8,192 bits. The UFM block connects to the logic array th

rough the MultiTrack interconnect,allowing any LE to interface to the UFM block. Figure 2–15

shows the UFM block and interface signals. The logic array is used to create customer interfac

e or protocol logic to interface the UFM block data outside of the device. The UFM block offer

s the following features:

■ Non-volatile storage up to 16-bit wide and 8,192 total bits

■ Two sectors for partitioned sector erase

■ Built-in internal oscillator that optionally drives logic array

■ Program, erase, and busy signals

■ Auto-increment addressing

■ Serial interface to logic array with programmable interface

UFM Block 官方资料 input output 介绍

MAX II UFM.pdf 第三页

一下是我觉得重要的几个IO:

三、 Oscillator

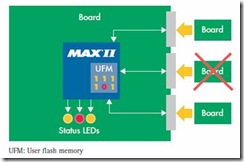

如上所示,可见MAX II系列CPLD,MAX II其实是内嵌了一块8Kbit 的Flash。

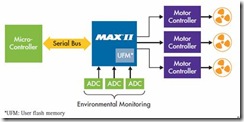

用户Flash存储器可用来存放ASSP和其它易失器件所需的初始化数据。用户Flash存储器替代了板子上小型的串行或并行可擦除可编程只读存储器(EEPROM)器件,从而减少了部件数量,降低了板子的成本。

这个Flash原则上是不占用MAX II的其它可用逻辑资源的,不过这有个大前提:用户读写这块存储区使用altera本身的串行接口(遵循特定的通信协议)。

下面是网上的人的一段评论:

“UFM中的OSCar产生13.33~22.22MHz的频率,经过4分频后,可以作为ARCLK或DRCLK的输入,或者可以通过接口输出到CPLD外部或引入逻辑阵列中,作为CPLD的工作时钟,4分频后为3.3MHz~5.5MHz,可以满足一般应用,虽然不能替代外部精准的晶振,不过在要求不高的场合还是可以使用,这样省下了外部晶振,节省成本。”

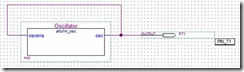

实际测试中,发现对Oscillator的控制有2种方法,直接Oscillator使能拉高或者Oscena Osc连接成反馈电路,具体在下面描述。

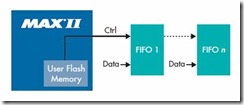

四、Altera UFM IP

在Quartus II 对于这块存储区读写接口altera提供了四种通用的接口供用户选择。

■ I2C

■ SPI

■ Parallel

■ None (Altera Serial Interface)

最后一种就是不需要占用器件额外逻辑资源的接口,上面三种是需要消耗器件逻辑资源的接口,在此我选择Parallel 并行传输模式,一是简单,而是高速,没必要去写SPI、I2C这些在verilog中书写复杂的协议。

五、Parallel 并行接口访问UFM ,并实现Water_LED

1. 新建工程

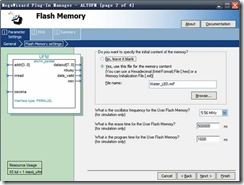

2. 在MegaWizard Plug-In Manager添加FLASH模块

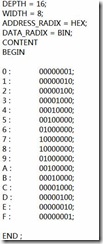

(1) 编写Water_LED的mif文件,存取在UFM中读取以实现流水灯的功能

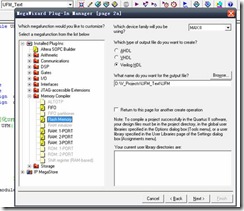

(2) Tool—Megawizard Plug-In Manager

(3)接着选择Memory Compiler下的Flash Memory,然后在What name do you want for the output file?下路径的最后添加输出文件名为UFM,点击next.

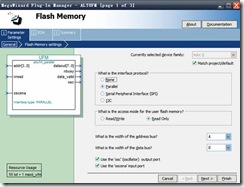

(4)选择并行Paralell只读模式

(5)

选择:

<1>晶振Oscillator:5.56MHZ或者3.33MHZ(再次测试我用的是5.56MHZ)

<2>擦除Flash的时间:默认500000ns

<3>Flash编程时间:默认1600ns

<4>在memory加入Water_LED.mif

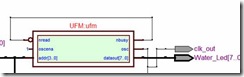

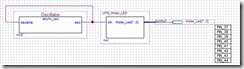

3. 编写UFM_Test.v程序

程序见文件UFM_Water_LED

UFM的读取基本时序为:

(1)nread 1->0;

(2)判断data_valid是否变高,变高则锁存数据do;否则等待;

(3)addr增1;

(4)nread 0->1;

(5) 重复以上操作

UFM接口模块实际上是在nread信号的上升沿锁存地址数据,在nread的下降沿开始读过程

4.分配引脚

set_location_assignment PIN_37 -to Water_Led[7]

set_location_assignment PIN_38 -to Water_Led[6]

set_location_assignment PIN_39 -to Water_Led[5]

set_location_assignment PIN_40 -to Water_Led[4]

set_location_assignment PIN_41 -to Water_Led[3]

set_location_assignment PIN_42 -to Water_Led[2]

set_location_assignment PIN_43 -to Water_Led[1]

set_location_assignment PIN_44 -to Water_Led[0]

set_location_assignment PIN_71 -to clk_out

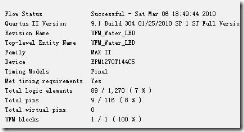

5.编译工程

如上图,真个工程只用了89个LE,以及UFM,没有占用其他让那个存储空间,没有使用晶振时钟,所有功能都在UFM内部实现。

6.JTAG下载

7.效果

8个LED灯 向左向右循环流动,但并没有用外部时钟。在Oscena Osc反馈电路回避直接Oscena快一倍的流动速度,原因是最后发现恰好倍频了。

六、发现的问题

1. UFM Oscillator

保证UFM内部晶振有2个办法:

一、给外部时钟源

二、时钟输入Oscena、输出osc直接接成反馈电路,不需要外部时钟振荡

三、直接把Oscena拉高

结论:

<1>经过再三测试,选择了第二种模式,可以省去晶振,但与Altera上的pdf讲的不一样,出来的 并不是3.3MHZ~~5.5MHZ而是10MHZ左右的时钟振荡

<2>Oscena 实际上就是Osc enable ,就是Osc时钟输出的使能,官方资料说:

“内部振荡器有一路输入OSC_ENA 和一路输出OSC。输入引脚OSC_ENA用于激活内部振荡器。激活后,输出上将产生频率为3.3 MHz 到5.5 MHz 的信号。如果振荡器使能信号OSC_ENA 被驱动为低电平,振荡器输出保持低电平不变。”

这样直接给1,实际始终出来的是5.15MHZ,和官方资料吻合。

一开始我都是直接用上面第二种反馈的方法的,但比官方说的倍频,现在想想可能就是刚好使能和osc的结合,恰好高低重返变换了一次,出现了二倍频吧,官方没有这种说法,我只能意会,不能言传,但出现官方的倍频确是有事实,而且貌似更稳定一点,又是一片新大陆。好玩!

2.IP核Flash与 Oscillator共用

实际工作发现这样不行,一直想不通,最后发现,Flash 和Qscillator两个IP核都是处理UFM内部模块的,可能在时序上有重合,不能同时驱动UFM,就像在verilog中,不同的进程中不能同时最同一个变量赋值,否则会出错

七、感受以及总结

每次编译CPLD 的工程的时候,最后都有![]() ,一直都看到,但是一直都不知道这是什么东西,现在终于明白了,以前一直没听说过,Google一下,网上还真有几个人在玩这个,不过仅仅是去teachbench一下。“哥伦布发现”,实际感受一下,原来那么好玩。

,一直都看到,但是一直都不知道这是什么东西,现在终于明白了,以前一直没听说过,Google一下,网上还真有几个人在玩这个,不过仅仅是去teachbench一下。“哥伦布发现”,实际感受一下,原来那么好玩。

不管是CPU还是什么东西,只要是处理器之类的东西,一般工作都是需要晶振来保证工作的,但CPLD内部神奇的UFM,原来那么好玩,让不可能变成了可能,让没有晶振的生活成为一种可能,在不需要时钟高度的精度和高速的时钟的情况下,可以省略去外部时钟,直接用内部时钟,不然,老是让传说中的UFM在神秘之中,未免浪费人才了。

利用Oscena反馈Osc,会出现官方5.5MHZ 的二倍频10MHZ,这个不错,官方没有这样的说法!

本人本次纯属兴趣,顺便搞清楚这一块,看看不可能有可能,可能在表达上不是那么的准确,但我提供的这是一种新思想,对不懂UFM 的人或许有帮助,虽然在实际应用中我们并不会用的太多,但是,物尽其所用吧。