FPGA/DSP背后的故事—退耦电容电路设计的探讨

0赞FPGA/DSP背后的故事—退耦电容电路设计的探讨

总结→不断的思考→这到底是为什么!!!!!

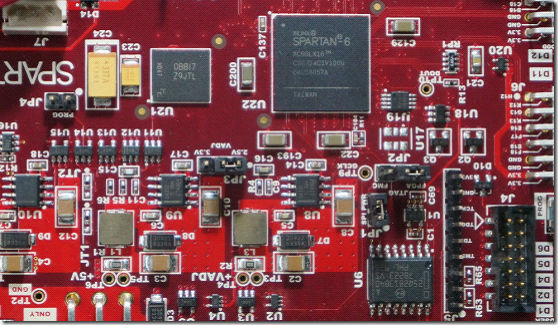

(1)LX16-Spartan-6

这是斯巴达6的板子,话说这电源这集的虽乱但看起来好牛逼的说,看看背后的故事:

斯巴达6的背后走了一个十字架式的去耦电容。

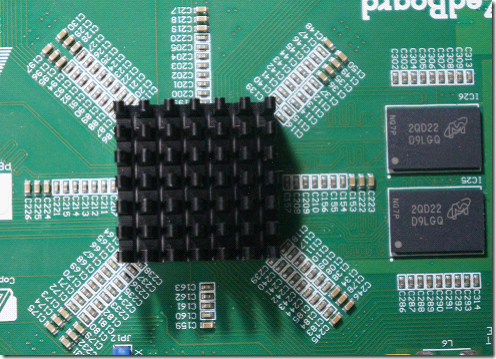

(2)DE2-35:

DE2-35 FPGA去耦,目测底部一块3.3V,然后20个0.1uF。中间应该是1.2V内核角落2个2.5V的去耦!

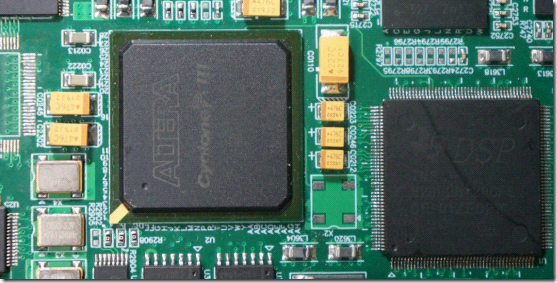

(3)TMS320C6748

接下来是DSP的板子,那左边一排DDR的电阻啊,为啥不用排阻。。。

它的背后是这样子的:

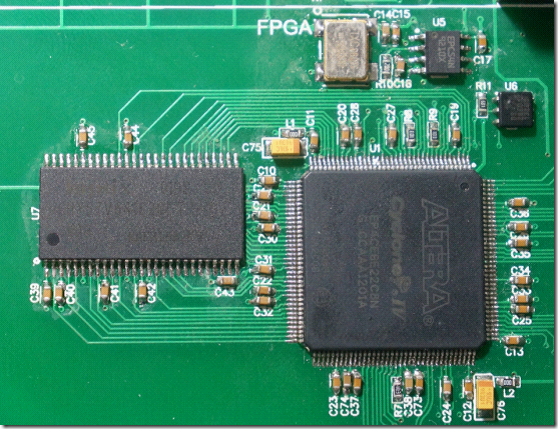

(4)ZedBoard

话说Xiliinx的开发板,总是有一种八卦的感觉,究其原因为啥这样设计呢?再看看背后,更加的八卦!!!但是肯定有设计者的道理!

(5)DE0-Nano

这又是Terasic的Nano板子,看起来他在每一个VCC上都放了去耦电容了!!!虽然这才256个IO。。。

(6)这是我们实验室的一个DSP+FPGA的处理板

他背后的故事是这样的:

推测应该是3.3V走了十字架,其他分布式电容!

(7)CIV-LCD

这是鄙人设计的LVDS-LCD的驱动板,因为背后是LCD所以所有期间都放到了正面!!力求做到了每一个VCC都放置了退欧电容,实现了1024*768@60Hz的LVDS LCD,但究竟是否科学,我不知道。。。。

(8)EP2C8-OV7670

这是我的一个OV7670的板子,顶层FPGA,底层每个VCC都设计了退耦电容。在功能上一直很OK,但是否还能优化呢,毕竟才跑到了130MHz!

电容的放置,对于辐射,文波,退耦,功耗等等等都有联系,曾经有一个工程师告诉我,他们的电容都是计算过的。而像我们这种半路出道的,实在不知道什么才是真谛!!!

看过EMC/ECI的书,模电也是略懂,相信大部分靠的是经验,希望有前辈能在这里给出众生指点!!!