【技术分享】04: CY7C68013 Slave FIFO及PCB设计

1赞1.1.1. 68013 Slave FIFO模式介绍

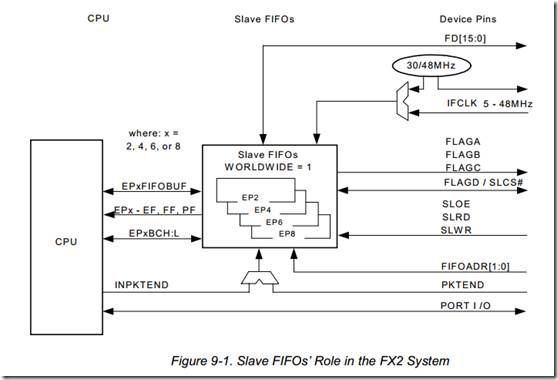

对于CY7C68013的通信接口而言,最主要的有GPIF与Slave FIFO。Slave FIFO模式是FX2最常用的模式。芯片工作于Slave FIFO模式下,该芯片就像一个USB FIFO。一端接USB口,另外一端就是一个简单的FIFO接口。USB的数据直接从上位机传递到该FIFO中,用户可以直接用现成的驱动程序和固件程序进行开发,省去了很多熟悉USB协议和驱动开发的工作。Slave FIFO通过内部的FIFO乒乓操作,实现数据的实时传输。其框图如下:

在Slave FIFO模式,68013与处理器只需要如下一个信号的链接,通过简单的片选,写入/读取实现,别可以实现数据的双向通信。

如下图所示,列出了68013 56脚封装的引脚。在后续的开发中,我们主要会用到Slave FIFO这个模式,因此关心Slave列表中的相关引脚。

Slave FIFO模式的CY7C68013 引脚配置及介绍如下:。

|

序号 |

引脚 |

定义 |

功能 |

|

1 |

|||

|

2 |

IFCLK |

USB_IFCLK |

最大48MHz,同步或者异步 |

|

3 |

SLCS/FLAGD |

USB_CS# |

片选使能信号,低有效 |

|

4 |

SLRD |

USB_RD# |

读取使能信号,低有效 |

|

5 |

SLWR |

USB_WR# |

写入使能信号,低有效 |

|

6 |

SLOE |

USE_OE# |

输出使能信号,低为输出 |

|

7 |

PKTEND |

USB_PKTEND |

包传输,暂时没用到 |

|

8 |

FIFOADDR[1:0] |

USB_ADDR[1:0] |

FIFO地址选择 |

|

9 |

FLAGA/CTL0 |

||

|

10 |

FLAGB/CTL1 |

USB_FULL |

输出,设置为低有效,FPGA捕获 |

|

11 |

FLAGC/CTL2 |

USB_EMPTY |

输出,设置为低有效,FPGA捕获 |

|

12 |

FD[15:0] |

USB_D[15:0] |

USB数据总线,可设置为8Bit或者16Bit模式 |

1.1.2. 68013 Slave FIFO PCB设计

(1)首先,我们需要提供一个心脏,及标配24MHz的无源晶振,作为时钟的输入,如下所示:

(2)同时,如果没有实现软配置,68013需要一个EERPOM作为FLASH存储器。标配的EEPROM主要有以下几个系列:

具体型号主要看系统,在CY7C68013A中,笔者常用的是24LC64反正也不贵。。。24LC64的原理图如下所示:

这里需要住的是A0引脚。当EEPROM非空白时,通常需要断开EEPROM,即将A0接地,来得到断开EEPROM的目的,使得系统不从EEPROM中启动,PC识别到NO EEPROM。在此时从新连接EEPROM,进行固件的更新。具体才做子啊后续中会给出

(3)USB接口设计

如上是笔者的第一版本USB接口电路图(后续持续更新)。其中保险丝是为了保护USB2.0免于短路之苦,而BAV99则是一定程序上对USB接口的过呀保护。1nF电容与1M欧电阻作为ESD保护的器件,系统通过USB直接供电。

(4)滤波电容的配置

为了实现电源的最大稳定性,滤波电容是最常用到的。这根FPGA的设计一样。。。。这里针对68013电源引脚,分配了如下几个电容:

(5)复位/唤醒引脚的设计

根据手册,默认上拉,电容接地。。

(6)数模电源的分配

DIY,呵呵,要求不是太高,数模不进行隔离问题也不大,采用磁珠/电感/电容进行隔离,搞不好还会生成LC震荡。这里偷个懒了呵呵。。

(7)最后,引出数据、RD、WR、OE等引脚,给出68013部分完整的原理图,如下所示:

对于CY7C68013的封装而言,有如下三种可选:

手工焊接第一种比较合适,对于产品而言,第二种更稍微更好的防止被抄袭。。。目测BGA封装的68013使用2层板子就能完成布线,问题不大呵呵。。Bingo一开始采用的是SSOP56的封装。目测在后续的版本中,会升级到BGA封装,偶尔装一下13吗,呵呵。。。

牛逼吹在前后了,这里先给出第一版的图,于Bingo在3个月前设计。。。最近心血来潮,打算升级成第二版,与大家一起分享,一起玩FPGA视频图像处理算法了。。。。