Bingo版HDL-VIP时序约定

0赞曾经Bingo写过CMOS的视频采集模块,即CMOS_RGB565_Capture模块(当然RAW、YCbCr模式的采集,接口不变),已经得到了以下的一组信号:

序号

信号

说明

1

clk (clk_pixel)

视频流像素时钟(当前为24MHz)

2

cmos_frame_vsync

采集后的帧有效信号

3

cmos_frame_href

采集后的行有效信号

4

cmos_frame_data

像素数据读取使能信号

(1) RGB565、YCbCr的时候,2个时钟一个数据

(2) RAW8的时候,一个时钟一个数据

(3) 如果灰度CMOS输入,亦一个时钟一个数据

5

cmos_frame_clken

像素数据读取使能,时钟分配同上

1. VIP_Image_Processor接口约定

从本章开始,我们全面进入HDL-VIP视频图像算法处理的开发,所有的算法模块均会包含在Video_Image_Processor模块。为了统一算法模块,以及视频流的接口,我们需要约定VIP时序,且称呼为《Bingo版的VIP时序约定》。这里先给出Video_Image_Processor模块的输入接口,如下所示:

|

序号 |

信号 |

说明 |

|

1 |

clk (clk_pixel) |

视频流像素时钟(当前为24MHz) |

|

2 |

rst_n |

全局时钟复位信号 |

|

3 |

per_frame_vsync |

预处理输入—采集后的帧有效信号 |

|

4 |

per_frame_href |

预处理输入—采集后的行有效信号 |

|

5 |

per_frame_data |

预处理输入—像素数据读取使能信号 (1) RGB565、YCbCr的时候,2个时钟一个数据 (2) RAW8的时候,一个时钟一个数据 (3) 如果灰度CMOS输入,亦一个时钟一个数据 |

|

6 |

per_frame_clken |

预处理输入—像素数据读取使能,时钟分配同上 |

注意,这里的per表示预处理的数据,当然经过视频图像算法处理过的时序,便称之为post_xxxx,如下表所示:

|

序号 |

信号 |

说明 |

|

1 |

post_frame_vsync |

处理后输入—采集后的帧有效信号 |

|

2 |

post_frame_href |

处理后输入—采集后的行有效信号 |

|

3 |

post_frame_data |

处理后输入—像素数据读取使能信号 (4) RGB565、YCbCr的时候,2个时钟一个数据 (5) RAW8的时候,一个时钟一个数据 (6) 如果灰度CMOS输入,亦一个时钟一个数据 |

|

4 |

post_frame_clken |

处理后输入—像素数据读取使能,时钟分配同上 |

此外,如果输入的是灰度图像,则命名为xxx_frame_Y,如果输入的是三通道RGB图像,则xxx_frame_red/green/blue,如果输入的是位图,则xxx_frame_Bit,详见下表:

|

序号 |

信号 |

说明 |

|

1 |

xxx_frame_Y |

输入/输出8Bit的灰度图像数据流 |

|

2 |

xxx_frame_red xxx_frame_green xxx_frame_blue |

输入/输出RGB888格式的数据流。 |

|

3 |

xxx_frame_Bit |

输入/输出1Bit位图格式的数据流。 |

此外,涉及到Video_Image_Processor输入的相关控制信号,比如各种阀值等,如下定义即可:

|

序号 |

信号 |

说明 |

|

1 |

Sobel_Threshold |

Sobel边缘检测外部阀值输入定义 |

这样,除了像素时钟与复位信号外,关于Bingo版的VIP时序约定、Video_Image_Processor的信号接口就已经有了一个统一的命名方式,且不管这个黑匣子的内容,在固定标准的模式下进行开发,更便于日后算法的优化、移植。这里给出8Bit灰度图像输入,1Bit位图输入,以及包含了一个阀值信号的Video_Image_Processor接口module,如下图所示:

`timescale 1ns/1ns module Video_Image_Processor #( parameter [9:0] IMG_HDISP = 10'd640, //640*480 parameter [9:0] IMG_VDISP = 10'd480 ) ( //global clock input clk, //cmos video pixel clock input rst_n, //global reset //Image data prepred to be processd input per_frame_vsync, //Prepared Image data vsync valid signal input per_frame_href, //Prepared Image data href vaild signal input per_frame_clken, //Prepared Image data output enable clock input [7:0] per_img_Y, //Prepared Image brightness input //Image data has been processd output post_frame_vsync, //Processed Image data vsync valid signal output post_frame_href, //Processed Image data href vaild signal output post_frame_clken, //Processed Image data output enable clock output post_img_Bit, //Processed Image Bit flag output //user interface input [7:0] Sobel_Threshold //Sobel Threshold for image edge detect );

2. VIP_Image_Processor时序约定

前面已经定制了Video_Image_Processor的接口,日后内部包含任何VIP算法模块,接口定义均与前面的约定保持一致,均以VIP_XXXX格式为准,XXXX表示功能,且保存于当前工程/src/Video_Image_Processor目录下。后续所有HDL-VIP的设计,都会遵循Bingo自己的约定。

既然接口已经标定,接下来最重要的就是约定VIP的时序。所有模块的输入输出,均遵循接下来Bingo约定的VIP时序,并且预处理输入接口的时序,与处理后输出接口的时序完全相同。这里就2种情况,进行时序的详细描述:

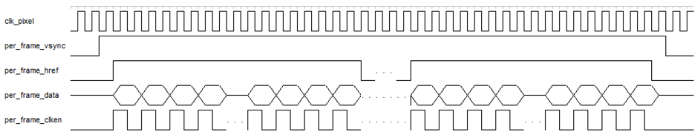

(1)时钟速率大于像素速率,如下图所示:

这种情况,正如前面OV7725输入24MHz像素时钟,但实际拼接后像素数据的速率为12MHz,时钟速率>数据速率。此时需要额外的per_frame_clken使能时钟,并且per_frame_clk有效边沿与数据的中间对齐。总之,使能时钟必须保证后续数据在clken有效边沿读取,一行640个有效边沿(根据分辨率变化)。

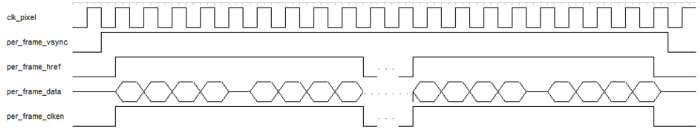

(2)时钟速率等于像素速率,如下图所示:

比如外部输入的是8Bit灰度数据,或者RAW阵列,此时时钟速率等于像素数据的速率,因此在行有效期间,clken信号一直有效,且保持640个有效周期(根据分辨率变化)。

post_frame_xxx,即视频输出时序,与输入时序(1)(2)2种情况完全相同,此处 不再做累赘阐述。根据以上两种情况,在经过任何算法处理后的数据输出,均因保持固定的时序,铭记Bingo版VIP时序约定!