【连载6.2.3.4】CY7C68013驱动电路设计

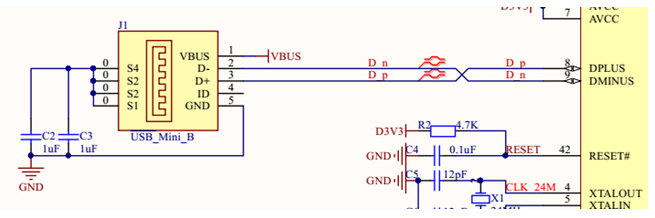

0赞CY7C68013的驱动电路非常简单,除了提供24MHz时钟源,设计好USB差分接口,做好电源滤波,其他信号均可由数字控制。这里简单的对Bingo设计CV7C68013A-56PVXC驱动电路进行介绍,如下所示:

(1)首先,USB差分电路设计的好坏,决定了实际能运行的速率。

Bingo采用USB-Mini接口进行68013的通信,同时完成板卡的供电功能。USB理论上能提供500mA的电流,2.5W的功率足够支撑板卡的工作。

在PCB Layout D+、D- USB差分信号线时,无比差分等长,保证信号完整性。此外,外壳通过1uF接地,简单而有效的进行了电路的ESD保护。

(2)采用24MHz无源晶振,如下所示。没有始终USB将无法识别。

(3)CY7C68013配置芯片24LC64 EEPROM

注意上拉电阻!

另外:如果EEPROM非空,或者说当前固件本机未安装驱动,可以通过通过按下KG1实现A0与GND的短路,从而让68013上电从内部启动。当然如果是全新的片子,那就无所谓了。

(4)复位引脚的配置

理论上68013的复位引脚直接高电平即可,但实际上Bingo经过多次的测试,发现RESET外接耦合电容,否则68013没有100%的成功率能完整正常启动,。这仅是Bingo的经验总结,因此这一部分电路千万不要偷懒,如下所示:

(5)坑爹的RESERVED设置

此外,最坑爹的RESERVED虽说是预留引脚,但是却不能NC。手册名门规定必须拉低,否则PC无法识别68013!

(6)WAKEUP功能时钟上啦,我们不做产品,不许睡觉!

(7)同步时钟IFCLK由外部FPGA输入,如下(12MHz输出可用与验证IC是否正常工作):

(8)所有控制信号都连接到了FPGA,如下图所示。其中FIFO地址可通过FIFOADDR选择;CS# OE# WR# RD#等控制信号直接接到了FPGA。PA0 PA1中断连接了FPGA;Full Empty输入给FPGA,如果要稳定不丢数据则需要配合这两个信号,否则FIFO有满或者空的风险。