EDK之路(6)——将ise工程封装成EDK下的IP(文件添加部分)

0赞 在上篇,我们给出了EDK下IP创建部分的说明。然而此时IP还只是一个空壳,我们接下来就将把我们的ise工程封进去。

(接上篇)

步骤二:修改及添加相关文件

文件结构图:

在修改以上文件以前,我们需要明白.mpd文件,led_flash_edk.vhd,user_logic.v,以及.v源文件之间的关系,才更能明白修改的要求与含义:

文件修改与添加:

1,.mpd文件,led_flash_edk.vhd,user_logic.v,的修改

这三个文件是固定的,不受上面提到的两种情况的影响,在这先修改这3个文件。

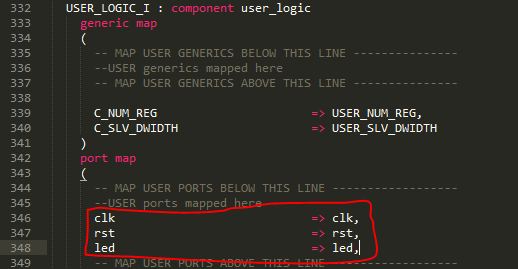

(1)user_logic.v的修改

(2)led_flash_edk.vhd

(3).mpd文件的修改

这里就涉及到前面所提到的两种情况了,这里将分情况讨论

情况一:只添加系统的wrapper文件,及其.ngc文件

(1)wrapp文件的添加:

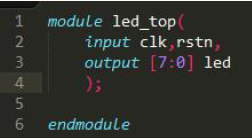

将顶层文件(led_top.v)复制到verilog文件夹中,并修改该文件,只保留端口信息:

(2).ngc文件的添加

首先先创建一个netlist文件夹,位置在文件结构图中有描述。

因为.v源文件只有一个顶层模块,此时顶层模块就是一个“黑盒”了,这就需要把顶层模块的.ngc文件添加到netlist。

注意:还需要把fifo, rom等自带IP的ngc文件也添加到netlist文件夹。ngc文件在相应IP的文件夹下。

(3).pao文件的修改

.pao文件即描述了IP所包含的源文件,由于刚添加了led_top.v,因此添加信息如下:

(4).bbd文件的创建

.bbd则描述了IP所包含的.ngc文件,该文件不存在,需自己创建一个“IP名.bbd”的文件。

这里创建一个“led_flash_edk_v2_1_0.bbd”的文件,里面加入信息如下:

情况二:添加所有.v文件

(1).v源文件的添加

把所有的.v文件(包括用到的fifo的.v文件)放到verilog文件夹中。verilog此时应包含如下文件:

user_logic.v

led_top.v

led_flash.v

clk_gen.v

led_fifo.v (fifo的.v文件,在生成的ip核目录下)

(2).ngc文件的添加

这里“黑盒”就不再是led_top了,因此不需要加入led_top的.ngc文件。现在黑盒是“led_fifo”,因此只需要加入led_fifo的.ngc文件

(3).pao文件的修改

(4).bbd文件的创建

3,语法检查

本操作可以检查hdl文件夹下的文件是否存在语法错误,不过对其余文件无能为力。其余文件只能通过xps来判断是否存在错误了。

打开devl->projnav下的ise工程,把verilog下的文件添加到工程里,然后检查语法,看是否发生错误

以上,文件的添加及修改完毕。点击xps工具栏project->rescan user repositories,使改变生效,如果相关文件存在错误,控制台会给出信息(如果工程较大,则给出信息的时间会较久)。

最后如果出现下面的错误,这就是前面所说的bug,就需要把上面提到的.ngc文件放到EDK工程目录下的implementation文件夹下。

补充说明:如果遇到上述问题,在.mpd文件中加入如下语句也可解决

到了这步,IP就创建成功了,可以成功产生相关硬件文件了(有时edk会出现文件没更新的情况,这时候就需要看文件的更改时间来判断改变是否生效了)