【再说FPGA】TSE-MAC的FIFO工作机制

0赞TSE-MAC的FIFO工作机制

最近在这条Altera三速以太网(TSE)的MAC,目前基本能够从这个挂在MAC上的Avalon-ST总线上收发PC的IP包了。

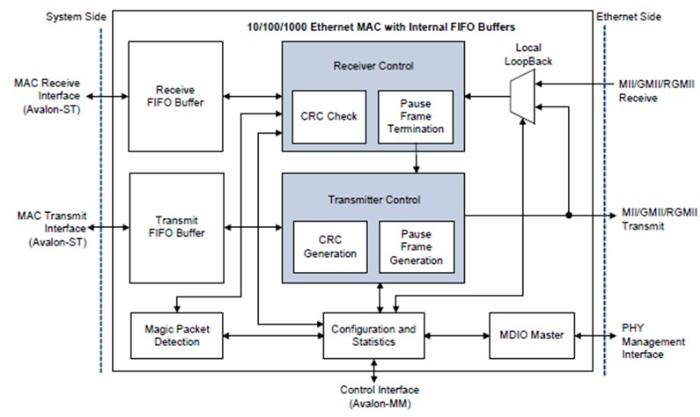

MAC是个试用版的IP核,内部框图如下。它通过MII/GMII/RGMII和FPGA外部的PHY交换数据。内部做了一些MAC该做的事,然后通过两个FIFO分别缓存以太网的收或发数据包。这两个FIFO读写的一端自然是MAC,另一端则是Avalon-ST总线。

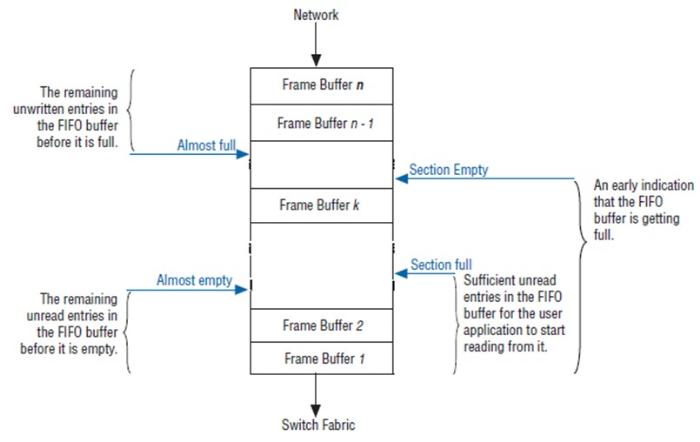

再说这两个FIFO的管理也很有学问,它要实现的功能是在尽可能不丢包(FIFO不能溢出或空读)的情况下收发数据。如图所示,这是RX FIFO用于控制的几个寄存器示意图。

这里有4个寄存器。User guide上有如下的描述。

光是看看这些枯燥的文字恐怕很难理解清楚它的工作机理。如果自己动手操作一把,遇上几次收发故障,那么再回头消化下估计就不难了。

简单的来看,almost empty和almost full是实际上MAC希望提醒Avalon ST总线或PHY端(也可以理解为远端的以太网设备)注意当前FIFO真得快full或empty了。当然了,almost empty有一种情况不会发出预警,那便是在FIFO中已经出现了当前收发帧数据的eop(end of packet),这种情况下会继续读FIFO直到eop;almost full预警发出时,如果读FIFO端仍没有准备好要读FIFO,那么当前帧可能就要遭受丢弃的厄运了。

与此类似,section empty和section full则不是绝对的FIFO的empty或full状况指示,个人的理解,这两个寄存器主要是设计者根据PHY端和Avalon-ST端的实际速率状况,相互提前做出指示,让另一方能够尽早做出相关操作的报警。Section full寄存器如果设置为0时,则使能store and forward模式,该模式下,完整的接收一整个帧的数据时则发起Avalon-ST的读操作。