【技术分享】以太网,FPGA就一定能搞定系列之芯片基本通信

0赞以太网,FPGA就一定能搞定系列之芯片基本通信

本系列博文节选自特权同学的FPGA开发电子书《SF-CY3 FPGA套件开发指南》。

最新设计文档下载地址:http://pan.baidu.com/s/1em79m

1 概述

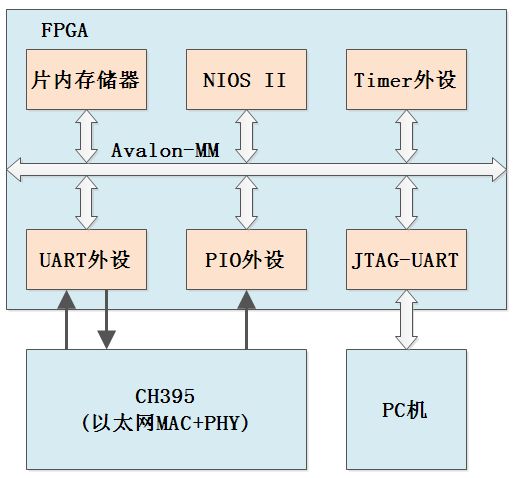

本实例的系统框图如图所示。后续的实验我们基本都是以此硬件架构为基础进行应用开发。NIOS II处理器和各个外设通过Avalon-MM总线进行互联通信,UART外设连接CH395的UART接口,进行命令和数据的传输交互;PIO外设连接CH395的中断信号,NIOS II处理器可以据此响应CH395的中断请求;JTAG-UART外设连接PC端的EDS软件,用于打印各种调试信息,便于我们追踪以及查看当前的板级调试状态。

在这个基础实例中,我们先不着急进行以太网的应用实例,只是简单的移植好CH395的底层驱动函数,并且打通UART通信,确认NIOS II可以通过UART正确读写CH395寄存器中的数据和指令。

2 Qsys硬件工程移植

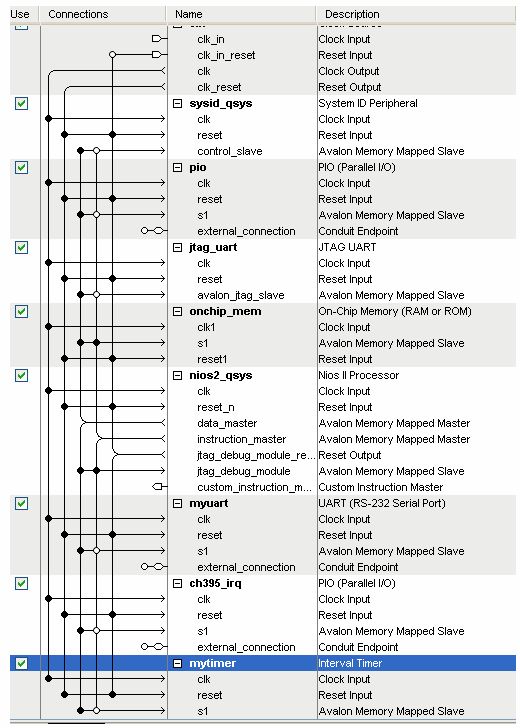

打开Quartus II工程,进入Qsys界面。我们除了使用NIOS II的UART外设进行CH395的基本通信外,还需要新建一个输入PIO的外设,作为CH395的中断引脚连接;再添加一个Timer外设作为NIOS II软件准确延时的基准时钟。

如图所示,这是该Qsys系统的各个外设组件及其相应的连接。

顶层源代码如下。UART外设的TX和RX分别连接到CH395的对应引脚上,输入PIO信号连接CH395的中断信号上。

module ex2(

clk,rst_n,led,

ch395_tx,ch395_rx,ch395_rst_n,ch395_irq

);

input clk;

input rst_n;

output led;

input ch395_tx; //CH395 UART-TX PIN_65

output ch395_rx; //CH395 UART-RX PIN_66

output ch395_rst_n; //CH395 RESET, ACTIVE LOW PIN_68

input ch395_irq; //CH395 Interrupt PIN67

myqsys u0 (

.clk_clk (clk), // clk.clk

.pio_0_external_connection_export (led), // pio_0_external_connection.export

.clk_0_clk_in_reset_reset_n (rst_n), // clk_0_clk_in_reset.reset_n

.nios2_qsys_0_custom_instruction_master_readra ( ), // nios2_qsys_0_custom_instruction_master.readra

.myuart_external_connection_rxd (ch395_tx), // myuart_external_connection.rxd

.myuart_external_connection_txd (ch395_rx), // .txd

.ch395_irq_external_connection_export (ch395_irq) // ch395_irq_external_connection.export

);

assign ch395_rst_n = 1'b1;

endmodule

分配引脚。编译新工程,将sof文件下载到SF-CY3核心板中。

3 软件设计

打开EDS软件,以当前硬件为基础创建空白工程,命名为ch395ex1_swprj。打开新工程的BSP Editor编辑界面,在Main页面的SettingsàCommon中做代码裁剪设置。

BSP的设置,主要是在开启必须的底层驱动的前提下,尽可能的裁剪代码量,从而确保有限的片内代码存储量得到合理利用。

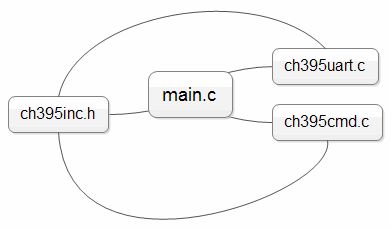

软件工程的基本架构如图所示,3个.c源文件,1个.h头文件。main.c用于编写主要的应用程序;ch395uart.c编写UART通信的各种基本函数;ch395cmd.c编写CH395各种命令和数据传输驱动函数,这部分基本是从官方提供的函数库中移植过来的;ch395inc.h对各个源代码中需要调用的各种函数做了申明,同时也对申明了各个需要用到的宏定义,3个C源代码文件中都包含了这个头文件。

官网上可以下载到CH395EVT.ZIP,这个压缩包中提供了CH375的底层驱动函数。但是要把它应用到NIOS II处理器中,着实还是要花点功夫的,好在特权同学将这个任务都搞定了,大家只要能够读懂datasheet,对各个命令的用处搞清楚即可,接下来的事情便是调用这些函数完成各种以太网的数据收发工作了。

CH395EVT.ZIP下载链接:http://www.wch.cn/download/list.asp?id=176

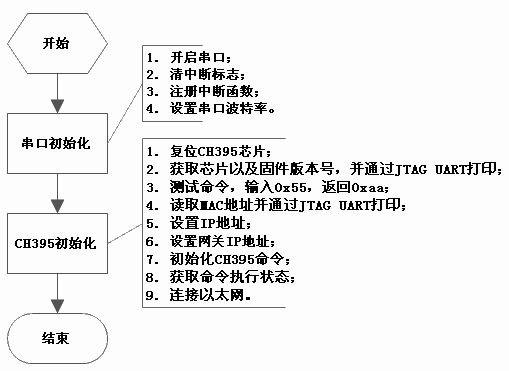

本实例的软件流程如图所示。CH395初始化中将通过JTAG UART打印出FPGA和CH395进行基本数据通信的信息。

4 板级调试

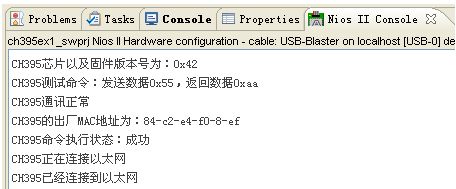

将硬件工程产生的下载配置数据流sof文件下载到目标板中,然后在线运行软件工程。稍等片刻,我们就可以看到在Nios II Console窗口中打印如图所示的CH395相关信息。