FPGA实战演练逻辑篇42:寄存器电路的设计方式

0赞寄存器电路的设计方式

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

上一章节中也已经基本介绍了寄存器的基本原型,在现代逻辑设计中,时序逻辑设计是核心,而寄存器又是时序逻辑的基础。因此,掌握时序逻辑的几种常见代码书写方式又是基础中的基础。下面我们就以图文(代码)并茂的方式来学习这些基本寄存器模型的代码书写。(特权同学,版权所有)

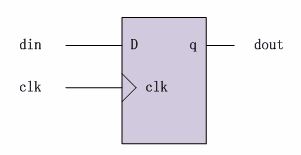

① 简单的寄存器输入输出的模型如图5.2所示。每个时钟信号clk的有效沿(通常是上升沿),输入端数据din将被锁存到输出端dout。(特权同学,版权所有)

图5.2 基本寄存器

基本的代码书写方式如下:

// Verilog例程

module dff(clk, din, dout);

input clk;

input din;

output dout;

reg dout;

always @ (posedge clk) begin

dout <= din;

end

endmodule

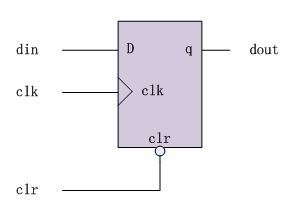

② 带异步复位的寄存器输入输出的模型如图5.3所示。每个时钟信号clk的有效沿(通常是上升沿),输入端数据din将被锁存到输出端dout;而异步复位信号clr的下降沿(低电平有效复位)将强制给输出数据dout赋值为0(不论此时的输入数据din取值),此输出状态将一直保持到clr拉高后的下一个clk有效触发沿。(特权同学,版权所有)

图5.3 异步复位的寄存器

基本的代码书写方式如下:

// Verilog例程

module dff(clk, rst_n, din, dout);

input clk;

input rst_n;

input din;

output dout;

reg dout;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) dout <= 1'b0;

else dout <= din;

end

endmodule

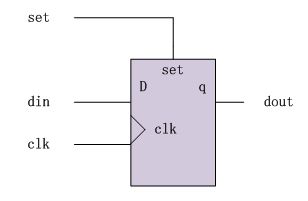

③ 带异步置位的寄存器输入输出的模型如图5.4所示。每个时钟信号clk的有效沿(通常是上升沿),输入端数据din将被锁存到输出端dout;而异步置位信号set的上升沿(高电平有效置位)将强制给输出数据dout赋值为1(不论此时的输入数据din取值),此输出状态将一直保持到set拉低后的下一个clk有效触发沿。(特权同学,版权所有)

图5.4 异步置位的寄存器

基本的代码书写方式如下:

// Verilog例程

module dff(clk, set, din, dout);

input clk;

input din;

input set;

output dout;

reg dout;

always @ (posedge clk or posedge set) begin

if(set) dout <= 1'b1;

else dout <= din;

end

endmodule

④ 既带异步复位,又带异步置位的寄存器则如图5.5所示。既带异步复位,又带异步置位的寄存器其实是个很矛盾的模型,我们可以简单的分析一下,如果set和clr都处于无效状态(set=0,clr=1),那么寄存器正常工作;如果set有效(set=1)且clr无效(clr=1),那么dout=1没有异议;同理,如果set无效(set=0)且clr有效(clr=0),那么dout=0也没有异议;但是如果set和clr同时有效(set=1,clr=0),输出dout咋办?到底是1还是0?

图5.5 异步复位和置位的寄存器

其实这个问题也不难,设置一个优先级不就好了。当然了,图5.5的理想寄存器模型通常只是作为电路的一部分来实现。如果我们期望这种既带异步复位,又带异步置位的寄存器在复位和置位同时出现时,异步复位的优先级高一些,那么代码书写方式可以如下:

// Verilog例程

module dff(clk, rst_n, set, din, dout);

input clk;

input din;

input rst_n;

input set;

output dout;

reg dout;

always @ (posedge clk or negedge rst_n posedge set) begin

if(!rst_n) dout <= 1’b0;

else if(set) dout <= 1'b1;

else dout <= din;

end

endmodule

这样的代码,综合出来的寄存器视图则如图5.6所示。(特权同学,版权所有)

图5.6 异步复位和置位的寄存器(复位优先级高)

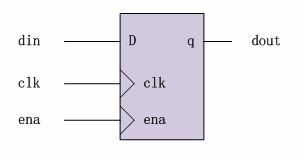

⑤ 如图5.7所示,这是一种很常见的带同步使能功能的寄存器。每个时钟clk的有效沿(通常是上升沿),判断使能信号ena是否有效(我们取高电平为有效),在ena信号有效的情况下din的值才会输出到dout信号上。(特权同学,版权所有)

图5.7 带同步使能的寄存器

基本的代码书写方式如下:

// Verilog例程

module dff(clk, ena, din, dout);

input clk;

input din;

input ena;

output dout;

reg dout;

always @ (posedge clk) begin

if(ena) dout <= din;

end

endmodule