FPGA实战演练逻辑篇59:VGA驱动接口时序设计之6建立和保持时间约束

1赞VGA驱动接口时序设计之6建立和保持时间约束

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

接着,我们可以对VGA的信号做如下的约束。(特权同学,版权所有)

set_output_delay -clock { LCD_CLK } -max 0.62 [get_ports {vga_b[0] vga_b[1] vga_b[2] vga_b[3] vga_b[4] vga_g[0] vga_g[1] vga_g[2] vga_g[3] vga_g[4] vga_g[5] vga_r[0] vga_r[1] vga_r[2] vga_r[3] vga_r[4] adv7123_blank_n}]

set_output_delay -clock { LCD_CLK } -min -1.28 [get_ports {vga_b[0] vga_b[1] vga_b[2] vga_b[3] vga_b[4] adv7123_blank_n vga_g[0] vga_g[1] vga_g[2] vga_g[3] vga_g[4] vga_g[5] vga_r[0] vga_r[1] vga_r[2] vga_r[3] vga_r[4]}]

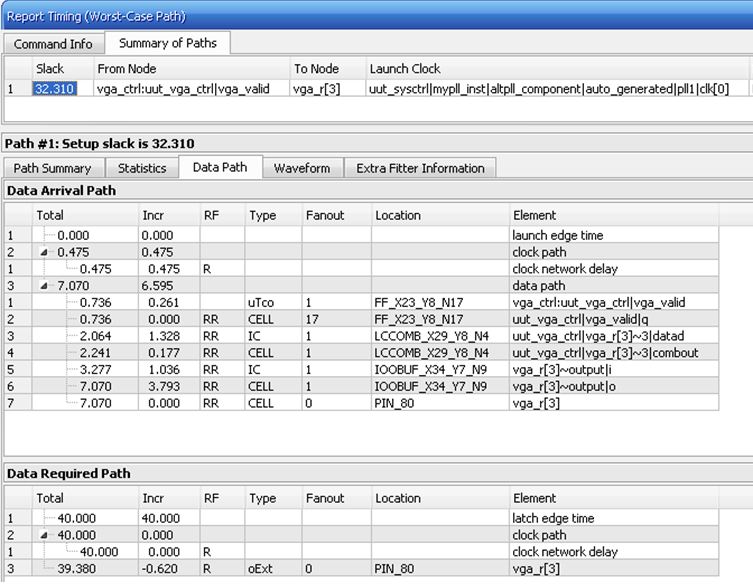

如此这般约束之后,我们可以重新编译一下系统,然后看看约束结果,我们拿到一条setup时间的分析报告。如图8.36所示,数据路径的分析没有啥问题,我们约束的0.62ns的max set_output delay值出现在了data required path中,说明我们的约束生效了。(特权同学,版权所有)

图8.36 某路径的setup约束分析报告

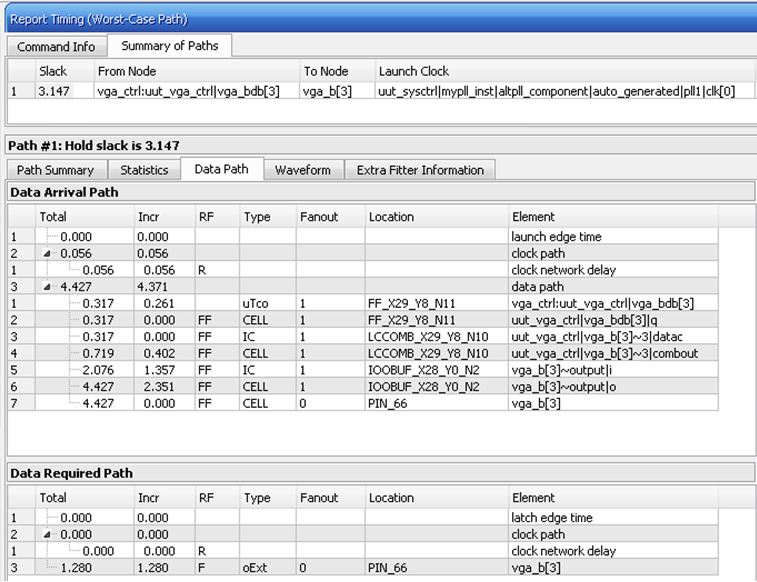

再来看hold时间的分析报告,如图8.37所示,也是随便找一条路径。-1.28ns的min set_output_delay也已经生效了。(特权同学,版权所有)

图8.37某路径的hold约束分析报告

即便如此,细心的读者一定没有忘记,前面的分析中我们忽略了时钟偏斜的延时值。没错,下面我们就要将它也考虑到路径延时中去。因为我们的lcd_clk直接就连接到了驱动FPGA内部模块的时序产生时钟信号,所以它的偏斜其实就是PLL输出的这个时钟信号到引脚的延时值。因为这个路径其实也应该算在了reg2pin的时序路径中,如果不做约束系统不会对其进行分析的。所以,为了获得这条路径的延时信息,我们势必需要对这条路径做一下约束。我们可以先试试将这条路径用set maximum delay和set minimux delay约束在0~5ns之间。set maximum delay和set minimux delay约束语法其实主要是用于我们前面所提到的第四类路径的约束,它非常直接的去约束信号的传输起点到目的点的路径延时值。我们的lcd_clk路径约束如下(注意我们所说的lcd_clk/LCD_CLK在FPGA代码中定义为vga_clk)。(特权同学,版权所有)

set_max_delay -to [get_ports {vga_clk}] 5.000

set_min_delay -to [get_ports {vga_clk}] 0.000

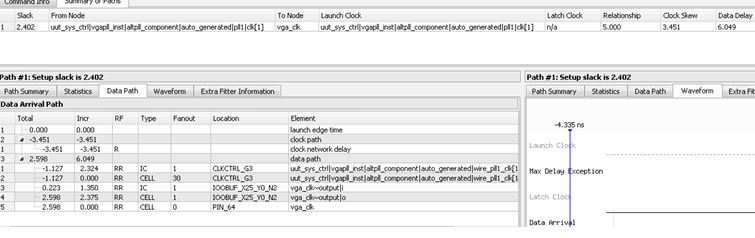

约束完成后,我们重新编译下系统,再来看看约束的结果。Setup时间余量最小的路径所对应的时序报告如图8.38所示。(特权同学,版权所有)

图8.38 setup路径余量最小的报告

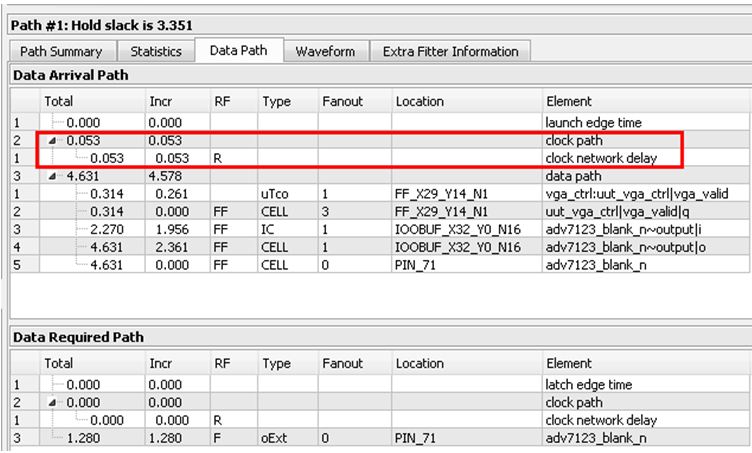

Hold时间余量最小的路径所对应的时序报告如图8.39所示。(特权同学,版权所有)

图8.39 hold路径余量最小的报告

从这份报告中,我们获得的信息是,从PLL的clk[1]输出到lcd_clk引脚的延时为2.116ns~2.598ns,那么给这个延时留一些余量,可以继续将他们的约束范围限制在2ns~2.7ns之间,即:

set_max_delay -to [get_ports {vga_clk}] 2.700

set_min_delay -to [get_ports {vga_clk}] 2.000

加上前面我们已经计算的lcd_clk在PCB上的走线延时,可以得到lcd_clk的偏斜时间约为2.44ns~3.14ns。留足余量,我们可以取lcd_clk的时钟偏斜为2.4ns~3.2ns。其实在比较严谨的系统中,通常用于给外部芯片的时钟信号要走FPGA的PLL输出专用引脚,并且也最好这个时钟信号是PLL直接输出供给的,满足这两个条件的时钟输出路径偏斜通常会被优化在一个非常小的范围里,而不会像我们这个设计一样出现理论计算这么宽的时钟偏斜范围(大家领会精神就行,这个时钟速率还不算太高,不用苛刻的约束去做也就能够满足我们的系统要求)。我们这个设计实际上也是PLL直接供给的,但驱动时钟并没有做相位差调整。如果整个lcd_clk连接到了FPGA的专用时钟输出引脚上,那么时钟偏斜会小很多,这也是之所以推荐走PLL专用输出时钟引脚的原因。(特权同学,版权所有)

接下来,我们需要将lcd_clk的时钟偏斜值代入output max delay和output min delay的计算公式。原公式中,cd_alt参数实际上都出现在了时序分析的launch edge的时钟网络延时中,如图8.40所示,所以我们无需再代入,直接取值为0ns即可。(特权同学,版权所有)

output max delay = 1ns + 0.2ns + (0ns – 3.2ns) = -2ns

output min delay = 0ns – 1.5ns + (0ns – 2.4ns) = - 3.9ns

图8.40 cd_alt参数示意

重新约束后脚本如下:

set_output_delay -clock { LCD_CLK } -max -2 [get_ports {vga_b[0] vga_b[1] vga_b[2] vga_b[3] vga_b[4] vga_g[0] vga_g[1] vga_g[2] vga_g[3] vga_g[4] vga_g[5] vga_r[0] vga_r[1] vga_r[2] vga_r[3] vga_r[4] adv7123_blank_n}]

set_output_delay -clock { LCD_CLK } -min -3.9 [get_ports {vga_b[0] vga_b[1] vga_b[2] vga_b[3] vga_b[4] adv7123_blank_n vga_g[0] vga_g[1] vga_g[2] vga_g[3] vga_g[4] vga_g[5] vga_r[0] vga_r[1] vga_r[2] vga_r[3] vga_r[4]}]